请教高手,这个差动三级振荡器为什么不起振

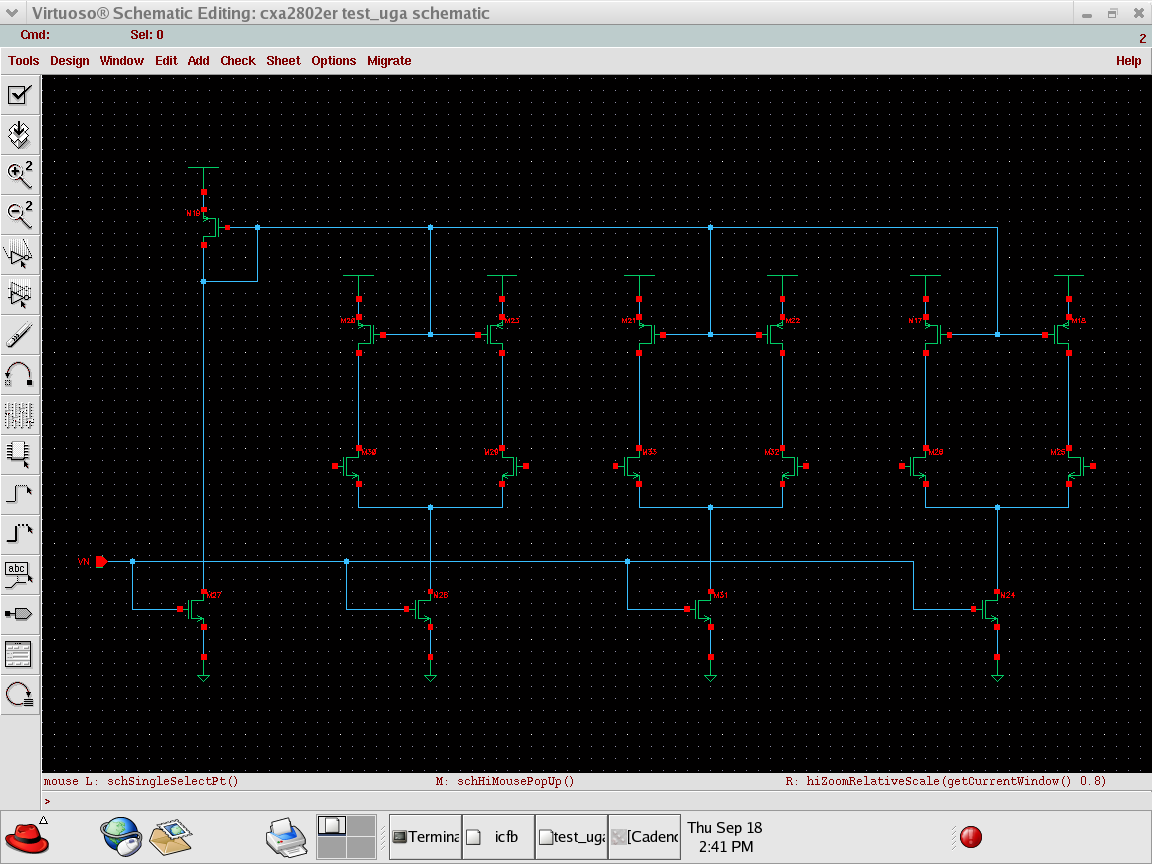

图1是修改前的振荡器的电路图,为简明没连级联线。仿真的时候各种情况都可以起振,但流片后大概有40%的芯片不起振 ,或者有时起振,有时不起振。

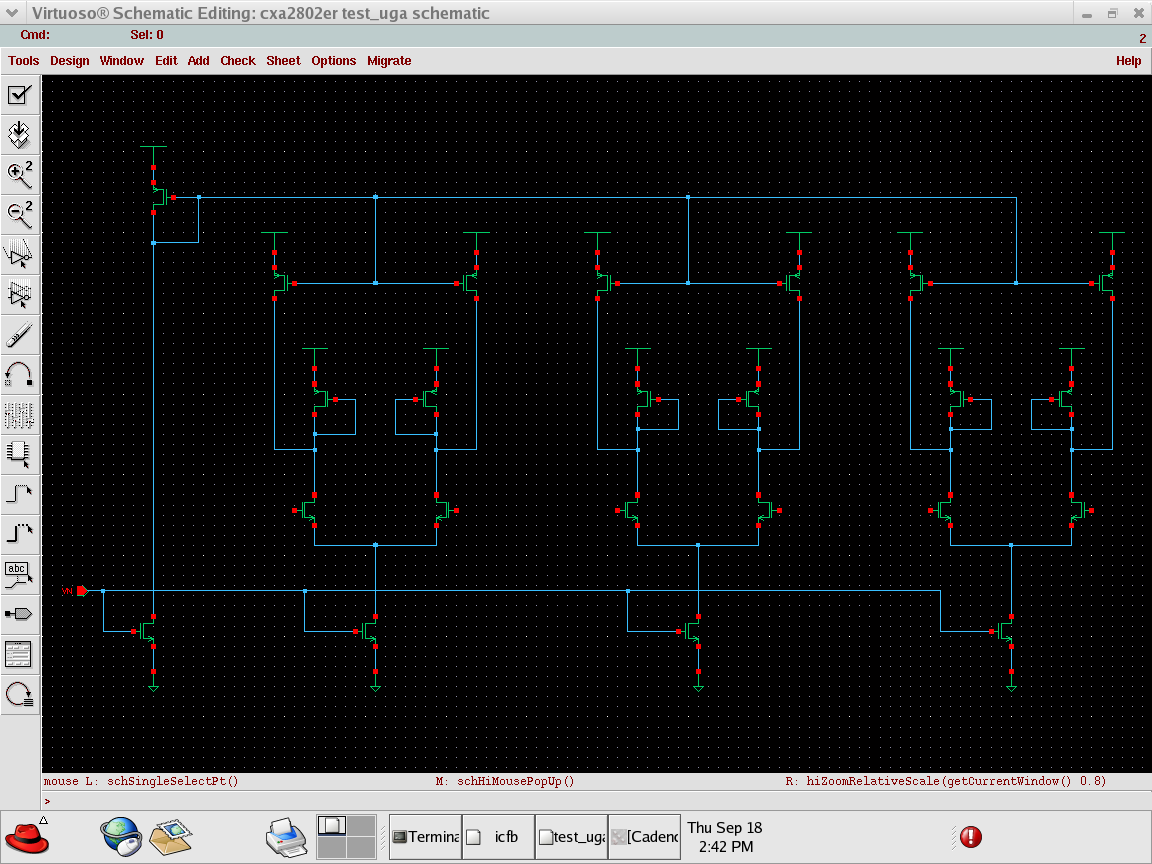

如图2经过修改,在每个cell中加入两个二极管连接的pmos管后,流片后就能全部起振了。我在论文上看到的这类差动振荡器上面的负载好像很少是纯电流源的。我想了好久好久都没想到原因。请教高手,这是什么原因啊!谢谢!

你看看Razavi中文版P48的例3.3,有没有帮助,我是菜鸟,没办法解答

这可能是与版图或工艺有关吧,不一定是电路的问题,另外,LZ 第一张图用的是电流源负载,如何去调整Td 阿。感觉有点怪异哦

书上p116图5.7有原型,其实为了改善增益的!

第一个工作点很难稳定,也就是说上电之后没能稳定在预设的工作点附近,不在放大状态,反而处于锁定状态,所以就不能起振了。

第二嘛由于二极管连接的存在,保证了各级放大器处于放大状态,所以就不存在这样的问题了。

总而言之 第二个结构可靠性比较好一点。在三级差动环振中,每一级的gain和phase都是要满足一定条件的

相当于每一级相移60deg,接回输入时看到一个反响信号,这样整个环路就起振

小编家了diode负载后,引入了diode的Cgs,每级相移加大,只要保证gain>2,整个环路就可以起振了

原来的可能相移太小也很感谢啦

每个cell的延时 = 输出端的电容 X 电流源的小信号电阻 , 开始的时候我是这样想的。

纯电流源负载应该增益更大才对啊你看看delay cell phase 60 度的时候,gain 是不是大于1

改善增益,并不一定非要使得增益变大!你这电路加了2级管负载后,输出端变成低阻抗极点!

仿真过了,delay cell phase 60 时候为40db

这位仁兄你真是天才!这个放大器的电流源理想是上下对称,但如果我把其中一个nmos电流源的尺寸改大5%的话,直流工作点就会太低,导致震荡停止。这个在hspice仿真里面已经得到了证明。就是说这个电路通过了各种工艺角和温度的仿真,但很可能过不了monte carlo 仿真。原因是mismatch,很小的mismatch就使理想直流工作点变化很大。问题已解决,多谢大家的帮助!

楼上及楼上的楼上分析的很好!

类似于CMFB作用,每级输出节点为差分高阻,只要mismatch

足够,就足以让电压偏移到一边锁定。加mos diode可把高阻降低,

设计mos diode尺寸以保证环路增益足够。