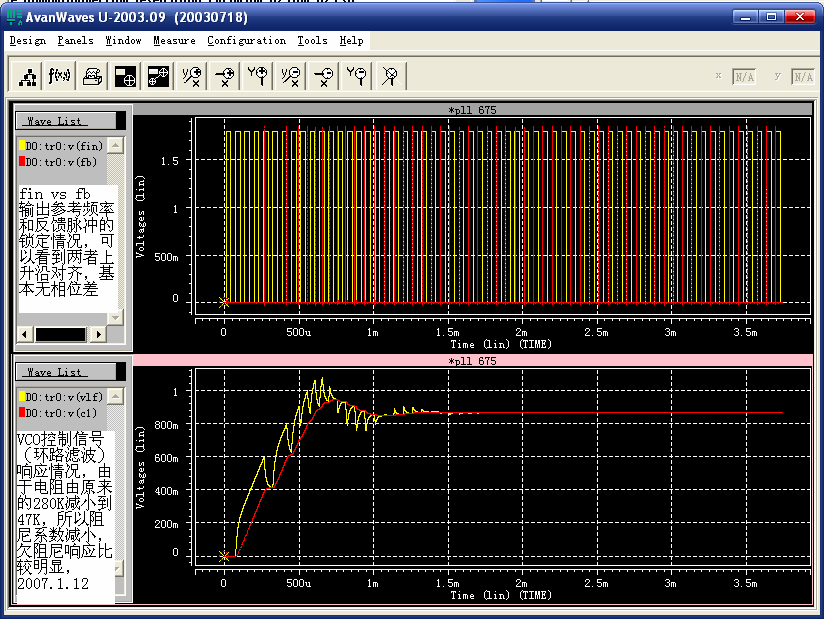

PLL的仿真结果(稳定过程)

时间:10-02

整理:3721RD

点击:

前些日子看见版上好多关于PLL的讨论,

以及稳定性方面的探讨

我1月刚开始做PLL,1月9号开始做电路级仿真

奔4太慢了,跑了3天

由于这个PLL的频率比较低,所以仿真时间也较长

感兴趣的朋友可以看看,提出一些宝贵的建议

还有,我的输入是方波,输出也是方波,

不知道怎么测相位噪声,用FFT吗?

但是方波的频谱本来就有很多杂波

我也一个一个测输出方波的周期,最大偏差<0.3%

呵呵,正常,我最长的跑过2个星期!你用的好像是spice;我们用的是CANDENCE,测相位噪声使用pnoise,测频率使用PSS,使用FFT不是很准确。我觉得,FFT只能测spur,测相位噪声还是要是用专门的工具哦。

close loop simulation, only get spur.

Keep in mind that an spectrum analyzer does not distinguish between phase noise and amplitude noise but shows the total power entering the filter passband from all sources.

问一下,你的PLL中的VCO是什么结构?

spectreRF是不是没法做PLL的相噪仿真?做做VCO的到是没问题.现在cadence 好像开发了一个仿PLL的工具,不过好象还没有正式卖,不知道准确度怎么样.也有人用cppsim仿,也不太清楚和测试结果吻合度怎么样?

模拟时间的长短和很多因素有关,PLL的结构,模拟的工具,工具中参数选择也会对模拟时间有很大的影响。

频率越高,仿真时间越长吧~

确实频率越高,仿真时间越长,我做的PLL是2。4G的,都跑5天了还没出LOCK,而且和LO一起跑时主意收敛问题!