CC2640R2从7x7封装换成5x5封装后编译后下载蓝牙无法连接。协议栈使用simplelink_cc2640r2_sdk_1_30_00_25

之前使用的是 CC2640R2 LaunchPad 开发板。蓝牙可以连接。

现在换成 自己的PCB版 芯片是CC2640R2 5X5封装。烧录后蓝牙无法连接,如下图片:

可以扫描到蓝牙,但是 连接后是空白。

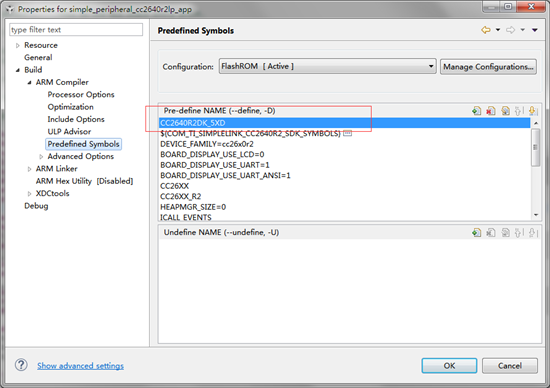

我的工程是CCS,我修改了宏定义如下:

把 CC2640R2_LAUNCHXL 宏删除,添加CC2640R2DK_5XD 宏。

如下代码也有修改:

const PIN_Config BoardGpioInitTable[] = {

IOID_11 | PIN_GPIO_OUTPUT_EN | PIN_GPIO_LOW | PIN_PUSHPULL | PIN_DRVSTR_MAX, /* LED initially off */

// CC2640R2_LAUNCHXL_PIN_GLED | PIN_GPIO_OUTPUT_EN | PIN_GPIO_LOW | PIN_PUSHPULL | PIN_DRVSTR_MAX, /* LED initially off */

IOID_3 | PIN_INPUT_EN | PIN_PULLUP | PIN_IRQ_BOTHEDGES | PIN_HYSTERESIS, /* Button is active low */

// CC2640R2_LAUNCHXL_PIN_BTN2 | PIN_INPUT_EN | PIN_PULLUP | PIN_IRQ_BOTHEDGES | PIN_HYSTERESIS, /* Button is active low */

// CC2640R2_LAUNCHXL_SPI_FLASH_CS | PIN_GPIO_OUTPUT_EN | PIN_GPIO_HIGH | PIN_PUSHPULL | PIN_DRVSTR_MIN, /* External flash chip select */

IOID_13 | PIN_INPUT_EN | PIN_PULLDOWN, /* UART RX via debugger back channel */

IOID_12 | PIN_GPIO_OUTPUT_EN | PIN_GPIO_HIGH | PIN_PUSHPULL, /* UART TX via debugger back channel */

// CC2640R2_LAUNCHXL_SPI0_MOSI | PIN_INPUT_EN | PIN_PULLDOWN, /* SPI master out - slave in */

// CC2640R2_LAUNCHXL_SPI0_MISO | PIN_INPUT_EN | PIN_PULLDOWN, /* SPI master in - slave out */

// CC2640R2_LAUNCHXL_SPI0_CLK | PIN_INPUT_EN | PIN_PULLDOWN, /* SPI clock */

PIN_TERMINATE

};

其他的我就没有修改了。

请问TI工程师 这是怎么回事?

另外我使用的是:simple_peripheral 工程

不同的封装需要更改设置,具体请参考这边: https://www.deyisupport.com/question_answer/wireless_connectivity/bluetooth/f/103/t/104028.aspx

我是先参考这篇帖字的,但还不行.

ble_user_config.h 头文件中标下面 宏定义需要改动吗?

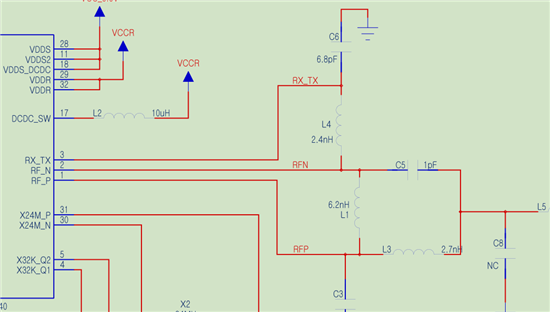

我的原理图部分如下:

#include "board.h"

// RF Front End Settings

// Note: The use of these values completely depends on how the PCB is laid out.

// Please see Device Package and Evaluation Module (EM) Board below.

#define RF_FE_DIFFERENTIAL 0

#define RF_FE_SINGLE_ENDED_RFP 1

#define RF_FE_SINGLE_ENDED_RFN 2

#define RF_FE_ANT_divERSITY_RFP_FIRST 3

#define RF_FE_ANT_divERSITY_RFN_FIRST 4

#define RF_FE_SINGLE_ENDED_RFP_EXT_PINS 5

#define RF_FE_SINGLE_ENDED_RFN_EXT_PINS 6

//

#define RF_FE_INT_BIAS (0<<3)

#define RF_FE_EXT_BIAS (1<<3)

// Tx Power

#define TX_POWER_5_DBM 5

#define TX_POWER_4_DBM 4

#define TX_POWER_3_DBM 3

#define TX_POWER_2_DBM 2

#define TX_POWER_1_DBM 1

#define TX_POWER_0_DBM 0

#define TX_POWER_MINUS_3_DBM -3

#define TX_POWER_MINUS_6_DBM -6

#define TX_POWER_MINUS_9_DBM -9

#define TX_POWER_MINUS_12_DBM -12

#define TX_POWER_MINUS_15_DBM -15

#define TX_POWER_MINUS_18_DBM -18

#define TX_POWER_MINUS_21_DBM -21

我从新clean 然后全部编译了一下工程就可以了