PCM1794解码器如何减少谐波失真

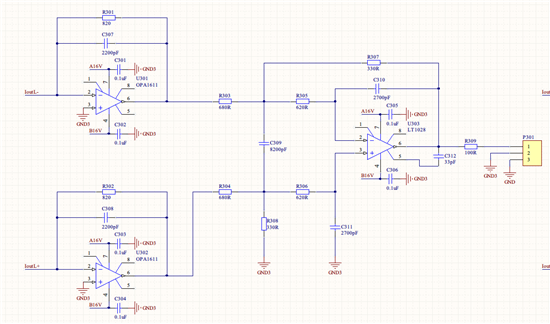

之前用PCM1794a和opa1611做了个解码器,IV和LPF电路使用的opa1611 datasheet上的电路,如下:

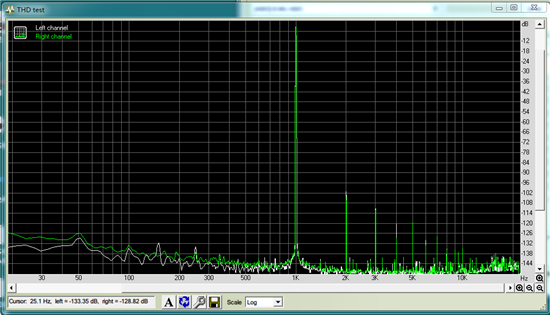

做了RMAA测试,其中谐波失真测试结果如下:

如图,1Khz以上谐波失真比较严重。

谐波失真是由什么地方引入的,如何减少呢,还烦请各位老师不吝赐教!

你好:

是这样的,但是2K,3K,5K相对于1K的信号还是比较小的。这个是带内的谐波,不好减少,因为要保证带内频点的信号不受影响。

有时候有些谐波,音乐听起来还更好听一些。从音色的角度来说不需要一味的去减少THD。

我这个测试出来的THD为0.0012%,但是很多人同样用1794都可以做到0.0006%

我很好奇到底是从什么地方造成的谐波失真,IV和LPF阻容网络的数值 还是PCB布线 还是电源的问题,我用的tps7a47xx和tps7a3301系列的LDO性能应该很不错了吧

你好:

测试出来的数据是THD+N,还会包含noise。你也需要比较底噪的大小。我不知道你做的电路和你所说的电路指标差异是THD还是Noise的差异,这两种都有可能的。

Harominc的成因我也不是很清楚,但是感觉器件本身的影响会比较大。

LPF的电容电阻的材料会影响,不知道你用的是什么样的电阻电容,精度如何?

从图上来看,已经做的很好啦

电容用的是0805封装的NP0电容,电阻用的是0805封装的1%精度电阻

谐波失真还是略高啊 应该可以再低一半的

您好,电容最好使用薄膜电容,电阻最好使用时最好实际量一下看误差是多少,一般可以采用0.1%的。你也可以尝试改变运放来看是否有效果,比如NE5534。

阻容数值应该对LPF的转折频率点影响比较大吧 对谐波失真的影响也很大么;

NE5534+LT1028我也试过了 谐波失真还会略大一些;

从论坛上看到有人说减小IV的补偿电容可以减小谐波失真 他还将LPF阻容网络的电阻变为十倍 电容减小十倍

这样做的原因是什么 会有什么副作用么;

另外 可以给我一份比较清晰的DEM-PCM1794评估板的PCB图么 想学习一下评估板的走线技巧

DEM-PCM1792, DEM-DSD1792, DEM-PCM1794, DEM-DSD1794 EVM User's Guide上的图看不清楚;

谢谢!

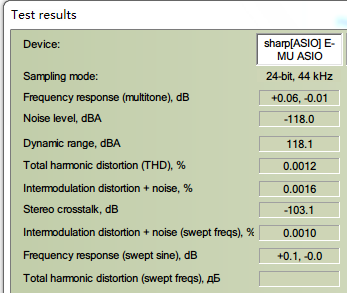

是THD不是THD+N

下图是具体的测试参数

不知道能否提供一份PCM1794的评估板的测试报告供参考一下

1. 谐波来源的本质是非线性,将传输函数的二阶三阶效应泰勒级数展开,就可以看到谐波的产生。

2. 非线性的来源一般来源于放大器,瓷片电容的压电效应也会产生一定的非线性。

3. 改善非线性的方法就是对称抵消,如果差动放大器可以做到完全对称,那么失真也可以降低,不单是器件,器件的性能,PCB布局布线都完全对称,所以对精度有要求,包括热对称。

增大阻可以改善非线性的原理是运算放大器在接不同负载下的失真不一样,一般10K左右的负载失真可以做到比较小,但是电阻太大会影响你的噪声特性。

所以电阻的值需要折衷。

你可以参考AYRE的QB9的线路图看看,也许会对你有帮助,这是一款输出端使用分立器件做的USB DAC。

你好是否能提供一下您所说的AYRE的QB9的线路图呢?因为在网上并没有找到相关的资料。