PCM186X 时钟问题

请教PCM186X的时钟问题,PCM186X在做从模式时,SCKI和XO,XI不接,使用BCK做时钟是否可以?

slave模式时,可以不外接MCK(SCKI),可以使用其内部PLL产生MCLK,而PLL的参考时钟来自BCK。

我使用的是PCM1862,输入4个通道,左右声道,一共8个输入,使用slave模式。

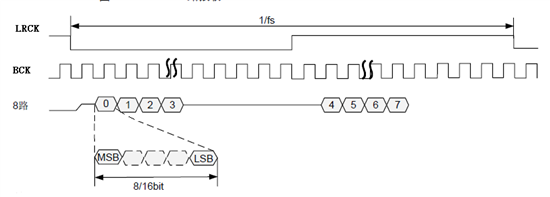

我自己的理解是LRCK和BCK之间的关系,应该是根据通道和位宽来决定的,如下图所示,如果8个输入,16位宽,那么BCK ratio to LRCK 就应该是128

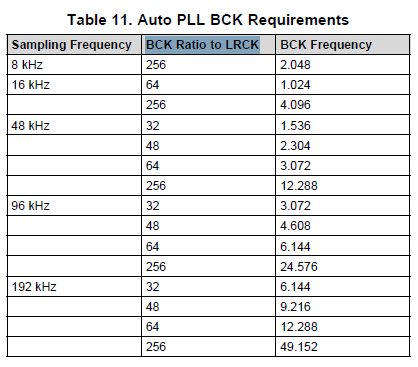

但是我在PCM1862datasheet上看到的,如下table 11所示,根本不考虑输入channel多少,位宽多少,BCK和LRCK之间是固定的。而且我设置pcm1862评估板,无论是一个通道,还是4个通道,无论是主模式,还是从模式,BCK和LRCK基本是不变的。为什么?

我需要4个channel,左右声道,采样率是8kHZ, 从模式,请问这个时钟怎么配置?

LRCK 就是采样频率,如果Fs=8KHz,那么LRCK=8KHz,按照Table11,BCK=64fs=1.024MHz。并且如果是64fs,那么传输的是32bit数据,左右通道各32bit。

同理,fs=48Khz,即LRCK=48KHz。

1, 您给的解释是单通道的时钟频率,

fs=8KHz,LRCK=8KHz,通道是32bit,那么BCK=左右各一通道共2通道*位宽*采样率=2*32*8=64fs=512KHz

您上面是1.024MHz,我得出的是512KHz,您算错了,还是我理解错了?

但上面的表格,采样率8KHz,LRCK=8KHz, BCK=2.048MHz,他是几个通道的?几位的,是不是32位,4个通道的?

2, 我需要的是4个通道的,每个通道都有左右通道

采样率是8K, 每个通道16bit,是不是LRCK=8KHz, BCK=8*16*fs= 1.024MHz?

另外有几个疑问:

1,我需要采集4个通道,是否不能用I2S模式,只能用TDM模式?

2,如果用TDM模式,时钟slave模式,分别4个左右通道,每个通道16bit,LRCK=8KHz, BCK==8*16fs=1.024MHz ,是否外部提供这两个频率的时钟就可以了?

前面的疑问请帮忙解答一下

你好,我现在也在用pcm1862。你当时的问题解决了吗?