TLV320AI3101录音断篇和失真的问题

你好,我们现在录音播放出来的声音频谱上可以明显看出有断篇和失真破音的问题。在比较嘈杂的环境 录音。

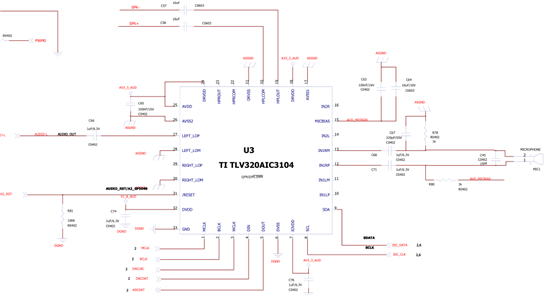

相关硬件接口如图,问题出在寄存器配置吗?这方面是菜鸟,请高手知道

你好:

录音听的得到明显的断音和破音吧?不仅只是从频谱上看。

录音的部分的电路没有问题。

软件上:

请问了你配置了AGC没 ? MICPGA的增益开的多大 ? 时钟部分怎么设置的。

hi flora wang

录音确实有明显的断音和破音,诚如频谱上一样!很明显。

能够告诉我,我对应的电路应该是要修改哪几个寄存器吗?

因为对各个通道和寄存器理解不深,能帮我看一下吗?,16bit如附件C代码寄存器

value = 0x60; // PGA Gain =59.5dB

//value = 0x0f;

tlv320aic3101_write(15, &value);

// value = 0xe0;

tlv320aic3101_write(16, &value);

2630.3101.txt

你好:

我看了一下你的寄存器,信息量比较大,主要看了一下你的PGA和AGC部分。

我建议这样:

1.PGA部分不要开的太大,你可以先写成00,然后离话筒近一点录音,PGA的增益太大,就容易录音破音。

2.AGC部分先不要开(先disable),先看下断音会不会消失。AGC的noise threshold设置的太大也会造成断音。

3.你的原理图上C67这处的电容,我不是很理解,请问为何要在这里加个电容呢?

4.下面的一个配置,发给你参考,可能和你的时钟部分处理的会有不同,我这个配置是只提供MCLK,其余的I2S时钟由codec产生,这个地方如果和你的设计不同你可以不参考。其余的,你可以对比看一下。

MCLK=12.288MHZ,Codec master:BCLK=2.304Khz, WCLK=48Khz

ADC MIC2/LINE2+DAC +HPLCOM

{0x02, 0x00}, //ADC/DAC fs=fsref/1

{0x03, 0x10}, //PLL disable,Q=2

{0x04, 0x00}, //PLL disable

{0x65, 0x01}, //CODEC_CLKIN=CLKdiv_OUT

{0x66, 0x00}, //PLLCLK_IN uses MCLK

{0x07, 0x0A}, //fS(ref) = 48 kHz;Left-DAC data path plays left-channel input data.Right-DAC data path plays right-channel input data.

{0x08, 0xC0}, //BCLK/WCLK output,master

{0x09, 0x20}, //I2S,16bit,Continuous-transfer mode

{0x0D, 0x80}, // 这里也配单端

{0x0F, 0x06}, //left ADC pGA unmute,PGA Gain=0db

{0x10, 0x06}, //Right ADC pGA unmute,PGA Gain=0db

{0x11, 0x0F}, //MIC2L/LINE2L Input Level Control for Left-ADC PGA Mix ,Gain=0 MIC2R/LINE2//R is not connected to the left-ADC PGA.

{0x12, 0xF0}, //MIC2L/LINE2L Input Level Control for Right -DC PGA Mix MIC2L/LINE2//L is not conndected to the right-ADC PGA.

{0x13, 0x7C}, //left ADC power on, 不连接MIC1

{0x15, 0x78}, //LINE1R is not connected to the left-ADC PGA.

{0x16, 0x7C}, //right ADC power on, 不连接MIC1

{0x18, 0x78}, //LINE1L is not connected to the right-ADC PGA.d

{0x26, 0x10}, //

{0x28, 0x40}, //Output common-mode voltage = higher output range, 1.5V

{0x29, 0x02}, //DAC to DAC_L1,DAC_R1,Left-DAC volume follows the right-DAC digital volume control register

{0x2A, 0x34}, //Power on delay=1ms,ram up 1ms

{0x3A, 0x6D},

{0x2F, 0x80}, // HP to L1

{0x40, 0x80}, // HP to L1

{0x41, 0x6D}, // power on HP

{0x33, 0x0D}, // power on HPL //

{0x36, 0x80}, // DAC_L1 is routed to HPLCOM

{0x3A, 0x0D}, // HPLCOM Output Level=0,HPLCOM is not muted

{0x44, 0x80}, // DAC_L1 is not routed to HPRCOM //0x00

{0x48, 0x0D}, // HPRCOM Output Level Control

{0x25, 0xE0}, //power on DAC

{0x2B, 0x00}, //LDAC umute,0db

{0x2C, 0x00}, //RDAC umute,0db

{0x33, 0x05},

{0x41, 0x05},

{0x2F, 0x80},

{0x40, 0x80},

{0x33, 0x6D},

{0x41, 0x6D},

{0x0E, 0xC0},