AIC3254的LOOPBACK实现问题

我用3254建立一个项目,配置为本地ADC TO DAC LOOPBACK(P0,R29.D4=1: Stereo ADC output is routed to Stereo DAC input)。发现在LOL和LOR输出端有比较大的噪音,信噪比很差。我怀疑是否有哪个地方设置不对,请问TI的工程师们能提供相关的设置和资料吗?关于它的本地LOOP BACK我有些地方真不是很明白,比如BCLK为何一定要设置为输出?不是没有使用外部的I2S总线吗?还有BCLK的分频器电源为何一定要打开?以及我修改过Bdiv(BCLK分频器)的时钟源,发现设置为DAC_CLK的时候它才有声音输出,我设置到DAC_MOD_CLK它就没声音输出了。这里让我觉得有问题。从手册上的时钟示意图来看,采样率的产生和使用跟BCLK是完全没关系的,不知道它为何会影响到音频。请帮忙解决一下问题,非常感谢。另外还请提供关于这个方面应用的更详尽的资料。

你好:

你提到的ADC TO DAC LOOPBACK是哪个设置,可否截图说明所在地址或者是贴出来设置。

我先了解一下你的配置需求,不知道你需要的资料是什么方面的?哪种应用?

AIC3254EVM的控制软件CS里有自带的一些配置,record,playback,都可以作为指导,很清楚,在此基础上根据应用的不同,稍作修改即可。还请参照已有的资料。

你好:

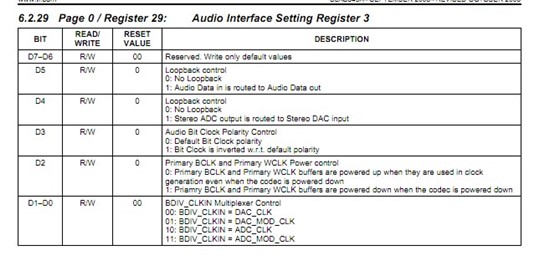

很感谢你的回答,我的项目中的ADC TO DAC LOOPBACK是通过设置在内部直接ADC TO DAC,而没有使用外部音频接口。这个选项在寄存器P0,R29的D4位,请看下面的图片

项目应用:

我想把AIC3254应用在前级信号驱动上,它处理的信号带宽是50HZ-18KHZ。这个项目要求的不失真输出信号电压幅度为1V(峰峰值)。

我用PurePath_Studio V5.95产生代码,然后通过外部控制器写入AIC3254。所有参数都是PurePath_Studio配置和产生的,我只修改了Bdiv和Audio Interface的相关设置。然而,在我这个模式下,直接下载PurePath_Studio 产生的代码AIC3254是不正常的,它没有声音输出。我手动加了两行代码,分别是设置WCLK和BCLK方向为输出,还有打开BCLK N Divider电源才正常,就这里我不明白。另外就是,我测试过LOL 和LOR的最大不失真输出信号幅度只有0.4V(峰峰值),就是下半周的底部到上半周的顶部幅度。这里跟手册所说的有很大差别。手册上说有0.375Vrms的,也就是1V的。差得太远了。由于它的输出信号幅度不足,所以我在外部加了一级增益为5倍的放大器,但是又带来了输出噪音略大的问题。恳请帮忙解答一下,谢谢。

你好:

PPS产生的代码,是个默认的配置,确实需要手动更改代码以匹配不同的应用需求。codec的配置很灵活,不同的应用有不同的需求,所以用户要自己配置。

LOUT的幅度不够,可以增加音量,一般音量默认都是0db,可以适当的增加。增加了音量,噪音也会增加,信号会一起放大,只要噪声不是很明显,这都是正常的。