PCM1754

hello,请教TI的专家:

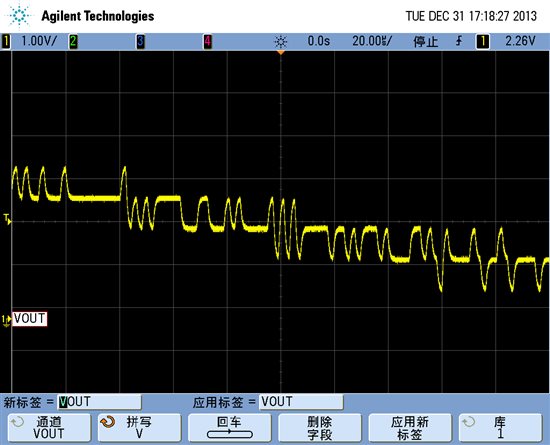

没有没有数据输入,但是音频输出如附件。

这是正常吗?

为什么会有这种现象?

该怎么解决?

你好,

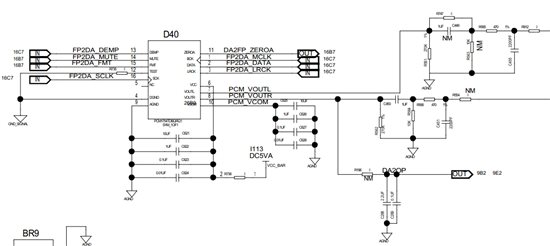

有没有原理图,发上来看一下?

谢谢!

你好,

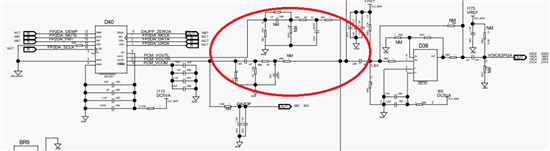

你的图有点模糊,你的图中L、R输出接在一起是什么用途?Mix吗?建议L、R输出再增加一级低通滤波,有源或RC无源都可,参见附件的一个demo电路图。

3857.TTK-PCM1754DBQ_RevA-Schematic.pdf

谢谢!

那个地方做了一个兼容电路。

我加2阶巴特沃斯滤波电路。

我现在主要疑问是:为什么没有数据的时候会有波形输出?

你好,

“我现在主要疑问是:为什么没有数据的时候会有波形输出?”

你的电路上可能还是有些问题的,正常情况下无I2S数据时,是不会有输出的。从你的波形上看貌似I2S Data直接串扰到输出上了。能不能发个清晰一点的电路图?

谢谢!

"NM"元器件没有焊接

没有数据传过去,怎么串到音频输出?

你好,

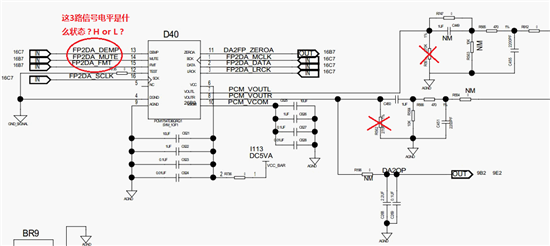

FMT、MUTE、DEMP引脚电平状态各是什么?

按照下图将输出电阻去掉试试。

谢谢!

demp = 0

fmt = 1

mute = 0

你好,

你主机端I2S格式是配成了16bit右对齐吗?一般来讲很少有用到这种格式的,一般应用都是16~24bit标准I2S格式。

谢谢!

对的

这种方式不能用吗?

可以用,只是让你确认一下。输出电阻去掉你试了吗?

试了,没有改善。

更换芯片有测试过吗?

几块板卡都是相同的问题。

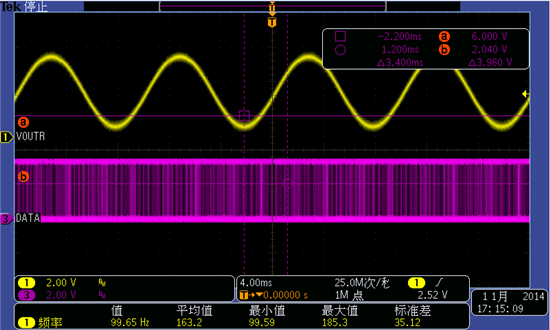

我做周期的正弦波,请帮忙分析一下。

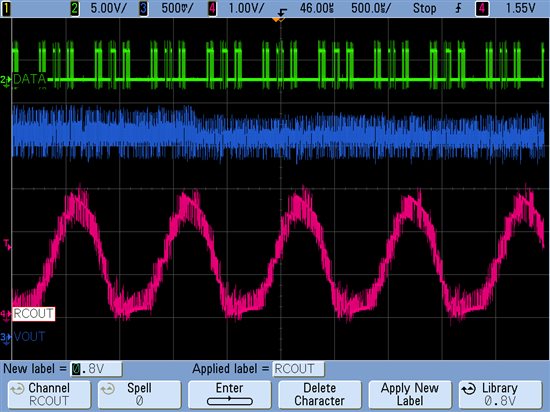

下图是波形:

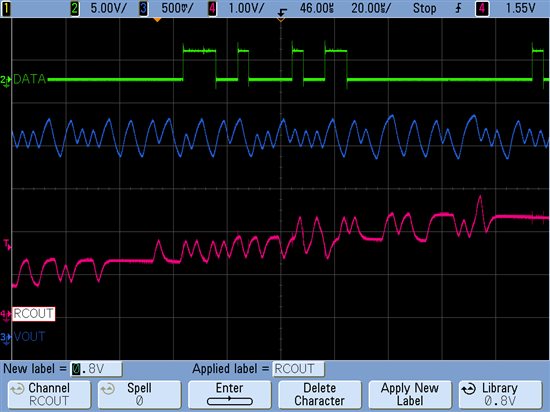

将上图展开如下:

你的5V电源是否干净,能否测一下纹波?

200mv

你的电源纹波太大了,好好把电源去耦和纹波处理下,电源线上串接个磁珠加强噪声过滤,电容靠近芯片管脚放置。

换了一路电源,纹波在10mv以下,现象一样,问题没有解决。

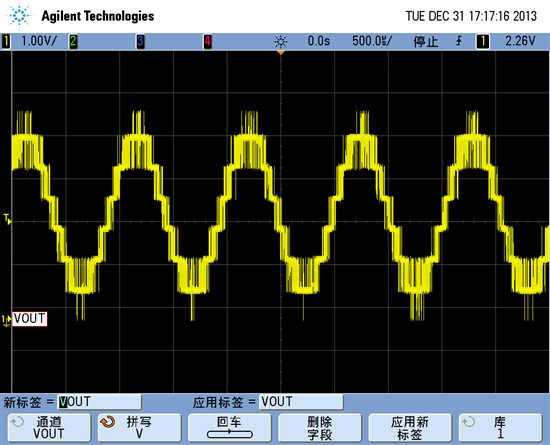

更换电源以后,测量PCM1754输出管脚,如下图:

注:叠加在正弦波上信号为128KHz或256KHz,请问这个是什么?怎么来的?该怎么去除?

你的MCLK、BCLK、LRCLK时钟频率各是多少?

16Bit Standardb标准格式:

SCk=2.048MHz

BCK=256KHz

LRCK=8K

使用I2S仍然存在相同的问题。

将Mute使能,音频没有输出,但是128KHz仍然存在,怎么回事啊?

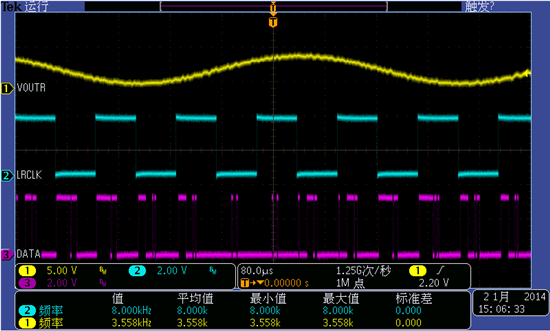

I2S配置如下:

FMT=0;

demp=0

Fs=8KHz

BCK=64*Fs=512KHz

SCK=512*Fs=4.096MHz。

不同的数据传输方式,存在相同的问题,还请TI的专家给出解答,谢谢!

我怀疑你I2S送的数据位太少了,可能都没有16bit,你可以看到你上面的一张图中DAC输出都呈阶梯状了,另外你的板子上干扰比较严重,时钟和数据边沿毛刺非常多。另外输出端RC低通滤波器截止频率在设低一点,你是用MCU自带的硬件I2S接口还是时序模拟的?

下图是我根据你上述条件实测的波形:

FMT=0

DEMP=0

Fs=8kHz/16bit

BCK=512kHz

SCK=4.096MHz

FPGA模拟的时序。

能把你的代码发给我嘛?

还有,硬件环境能借我们调试一下吗?

抱歉,我不是用的FPGA,硬件也非常简单,就是一个PCM1754最小系统板加Audio Precision产生I2S信号。

因为PCM1754就是一个DAC,硬件电路上不会有太大问题。你的问题就是出在FPGA时序模拟上,I2S对时序要求非常严格,LRCLK、BCLK、MCLK(SCLK)要求和数据要保持同步,你的FPGA代码中可能还是有些问题。下面链接是I2S在FPGA上模拟的参考例子,Altera和Xilinx的都有,你参考这个来试试:http://opencores.org/project,i2s_interface,synthesis

能将波形展开看看吗(1个周期)?

怎么会一直有数据呢?

有效数据16Bit,BCK=64Fs(32bit),不是应该周期性有数据吗?

请帮忙附上SCK、BCK、LRCK、VOUT对比图(最好能够有局部展开的图形)。

谢谢!

找了一块PCM5100的Demo板,然后将FPGA的时钟线、数据线连接到Demo,输出的波形很正常,没有128KHz和256KHz的成分混在里面,所以模拟的I2S时序应该不会存在问题,可能还是PCM1754自身的问题。

专家,支持一下我们吧,谢谢!

如果是PCM1754芯片的问题,通过交叉试验你很容易验证出来,另外我也帮你测试过相同条件下输出波形是没有问题的。现在的问题是你们几块板子都是出现相同的问题,所以还是先要从电路和其它外围查起。

PCM5100验证时你有没有接MCLK?另外PCM5100内部自带PLL,当你的MCLK出现问题或不接时,会自动切到PLL时钟。

你的FPGA代码中BCLK和LRCLK都是如何来的?是和MCLK从同一个时钟源分频出来的吗?

你方便把你的PCB截图也发上来看看吗?

这个跟I2S的时钟会有一定关系。时钟不是12M时会输出噪声

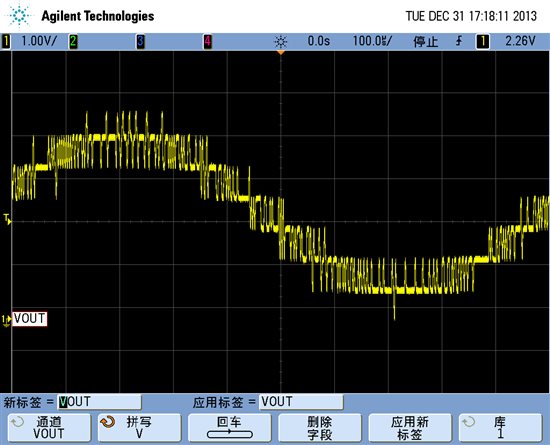

VOUTR、LRCLK、DATA截图如下:

所有数据、时钟都是一个时钟源,然后我使用153.6MHz主时钟(其他时钟也是从这里分出来的)同步了。

系统时钟153.6MHz,分出DAC的SCK、BCK、LRCK等

请教一下,如果我输出到PCM1754的16为数据为0(即DATA引脚一直是低电平),此时Vout应该输出什么?是2.5V的直流吗?

Mute使能以后,怎么也会存在128KHz和256KHz?

“请教一下,如果我输出到PCM1754的16为数据为0(即DATA引脚一直是低电平),此时Vout应该输出什么?是2.5V的直流吗?”

是的,2.5V偏置电压。

你先这样测试一下:

断开PCM1754与FPGA的所有I2S连接,只给PCM1754上5V电压,不Mute,看输出是否是没有任何干扰的2.5V偏置电压。

只要没有SCK、BCK中任何一个时钟,就不会有噪音。

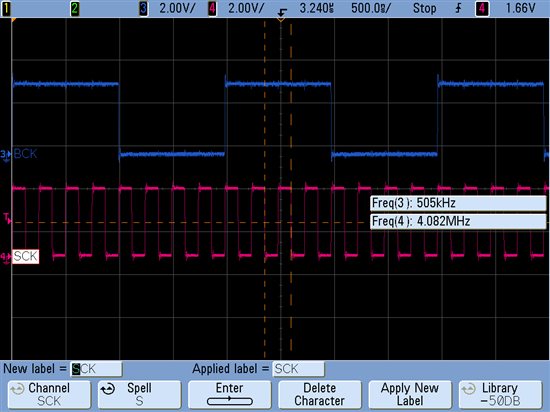

能把你的SCLK、BCLK同时在示波器里抓一下,放大贴上来看一下吗?主要看看SCLK、BCLK噪声和同步情况。

SCK、BCK对比如下:

请问一下,能将你们那一套测试环境借给我们使用一下吗?

你们在哪,上海吗?上海这边有没有实验室,也可以去贵公司做实验,对比一下。

方便的话,请给我留个联系方式,我的邮箱:zhangcong_zone@163.com

谢谢!

不好意思,我不在上海。我可以借你一块我测试用的PCM1754的最小系统板,你再验证一下。附件是该板的User's Guide:

5468.Tiny Tool Kit(TTK)-PCM1754DBQ User's Guide - Done.pdf

你把你的地址和联系方式发我邮件: pengjie-wang@ti.com