请教关于TLV320AIC3101使用中的一些问题

我最近正在用FPGA做TLVADC3101的驱动,碰到不少问题,本人是新手,能力有限,固有些问题不能解决,特来此请教各位大虾,希望能够得到各位的帮助,在下不胜感激,在此先行谢过!

控制方面,现在FPGA已经可以通过I2C总线对AIC3101的内部寄存器进行配置。语音数据交互方面,将AIC3101作为主设备,采用I2S的数据交互方式。FPGA的工作时钟为44MHz,并将此时钟作为MCLK由FPGA输入给AIC3101。WCLK和BCLK则由AIC3101通过内部PLL产生,并由AIC3101输出给FPGA。ADC/DAC采样频率为48KHz,数据长度32bit,配置PLL的P.R.J.D值为:P=3, R=1, J=6, D=7025。麦克风从MIC2L单端输入(或MIC2L与MIC2R双端),内部连接到左右声道,经过PGA 0db 放大后 音频直接输出到HPROUT(HPROUT/HPRCOM或HPLOUT/HPLCOM)。

具体的内部时钟寄存器配置如下:

一、44MHz系统主时钟(MCLK)输入,使用PLL,ADC/DAC采样频率为48KHz,配置PLL的P.R.J.D值为:P=3, R=1, J=6, D=7025,具体的寄存器配置如下:

WrData(0,0x00);

WrData(01,0x80); //软件复位

WrData(101,0x00); //使用PLL来产生codec内部时钟(reg 101)

WrData(07,0x0A); //选择48KHz参考采样频率(reg 7),L-DAC播放I2S-L输入信号, R-DAC播放I2S-R输入信号

WrData(03,0x93); //允许PLL,P=3(reg 03)

WrData(04,0x18); // J=6(reg 4)

WrData(05,0x6D); // 6D为D值的高8位

WrData(06,0XC4); // C4为D值的低6位

//配置音频接口主模式,数据字长32位,I2S格式

WrData(08,0x D0); //接口主模式,即使在ADC以及DAC POWER Off时BCLK/WCLK仍有输出

WrData(09,0x37); //32bit,I2S格式,连续BCLK时钟输出模式,允许重新同步

二、音频I2S接口寄存器配置

//配置音频接口主模式,数据字长32位,I2S格式

WrData(08,0x D0); //接口主模式,即使在ADC以及DAC POWER Off时BCLK/WCLK仍有输出

WrData(09,0x37); //32bit,I2S格式,允许重新同步

三、语音输出寄存器配置

//3.3V CODEC 电源, HPLOUT/HPROUT电容型输出

WrData(14,0x80); 电容型输出(Reg 14)

WrData(40,0x80); 输出直流偏压电压设定为1.65V(Reg 40)

WrData(42,0x8E); 输出级上升延时400ms,信号上升时间4ms(Reg 42)

四、ADC通道寄存器配置

//单端MIC从AIC31的 MIC2L/LINE2L输入。MIC偏置电压为2.5V,放大增益为26dB。I2S L/R通道同时输出麦克风信号

WrData(25,0x80); 麦克风偏置电压为2.5V(reg 25)

WrData(17,0x00); 连接MIC2L到 L-ADC PGA,MIC2设置为单端输入模式(reg 17)

WrData(18,0x00); 连接MIC2L到 R-ADC PGA(reg 18)

WrData(26,0x80); enable left AGC(Reg 26)

WrData(15,0x34); // left ADC PGA not mute,L-ADC PGA增益设定为26dB (reg 15)

WrData(27,0x68); // left AGC 增益设定为26dB (与L-ADC增益一致) (reg 27)

WrData(29,0x80); // enable right AGC(Reg 29)

WrData(16,0X34); // right ADC PGA not mute,R-ADC PGA增益设定为26dB(Reg 16)

WrData(30,0x68); //right AGC 增益设定为26dB (与R-ADC增益一致) (reg 27)

WrData(19,0x7C);// L-ADC上电(Reg 19)

WrData(22,0x7C); // R-ADC上电(Reg 22)

五、DAC模拟输出通道寄存器配置

//Stereo Headphone, Stereo external audio amplifier

WrData(37,0x E0); L-DAC/R-DAC上电,HPLCOM独立单端输出(reg 37)

WrData(41,0x01); L-DAC选择DAC-L1,R-DAC选择 DAC-R1,左通道DAC数字音量跟随右通道音量值(reg 41)

WrData(43,0x00); //设置L-DAC数字音量=0dB。(reg 43)

WrData(44,0x00); //设置R-DAC数字音量=0dB。(reg 44)

WrData(38,0x10); //寄存器设置值. 允许PLL,P=3(reg 03)

WrData(51,0x0D); // HPLOUT上电非静音,电平设置= 0dB(reg 51)

WrData(47,0x80); / HPLOUT通道模拟音量设置,DAC-L1引入到HPLOUT,音量= 0dB(reg 47)

WrData(46,0X80); // PGA_L to HPLOUT, 0db,音量=0dB(reg 46)

WrData(58,0x0D); // HPLCOM上电非静音,电平设置=0dB(reg 58)

WrData(54,0x80); // HPLCOM模拟音量设置, DAC-L1引入到HPLCOM,音量=0dB(reg 54)

WrData(65,0x0D); // HPROUT上电,非静音,电平设置=0dB(reg 65)

WrData(64,0x80); // HPROUT模拟音量设置,DAC-R1引入到HPROUT,音量=0dB(reg 64)

WrData(63,0x80); / /PGA_R to HPROUT, 0db,音量=0dB(reg 63)

WrData(72,0X0D); // PGA_L to HPLOUT, 0db,音量=0dB(reg 46)

WrData(71,0x80); / / HPRCOM模拟音量设置DAC-R1引入到HPRCOM,音量=0dB(reg 71)

WrData(107,0X08); // ADC digital output to programmable filter path

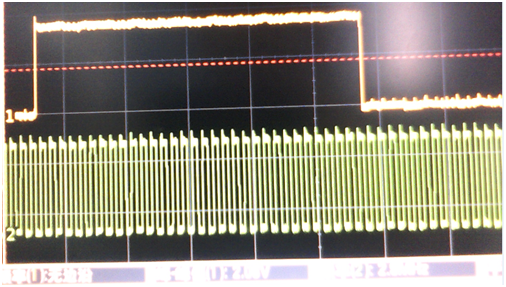

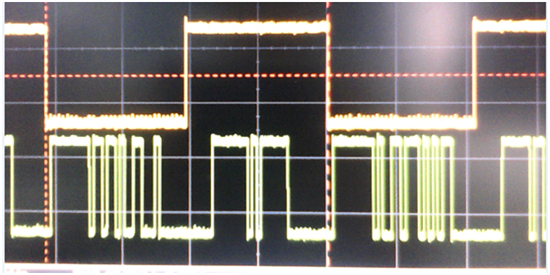

由以上的配置,可以得到一些结果:通过示波器,可以观察到产生的WCLK为48KHz,BCLK为3.07MHz。符合期望值,具体如图1所示

图1 AIC3101的WCLK(上)与BCLK(下)管脚信号

在图1中,WCLK的一个高电平内,有32个BCLK时钟数目,亦即一个WCLK中BCLK时钟数目= 2X数据字长,若将32改为16,BCLK的数目也将相应的改变。这与数据手册上所描述的一致。

但是输出端却没有任何声音,所以我的主要问题就是:

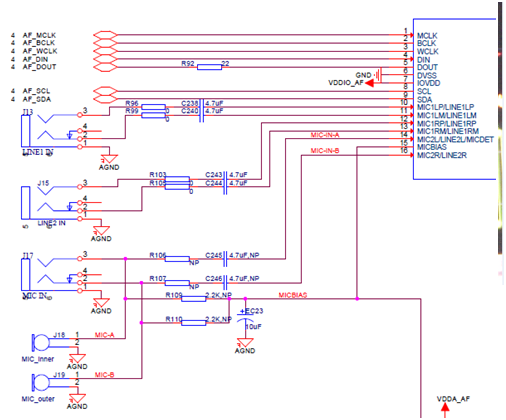

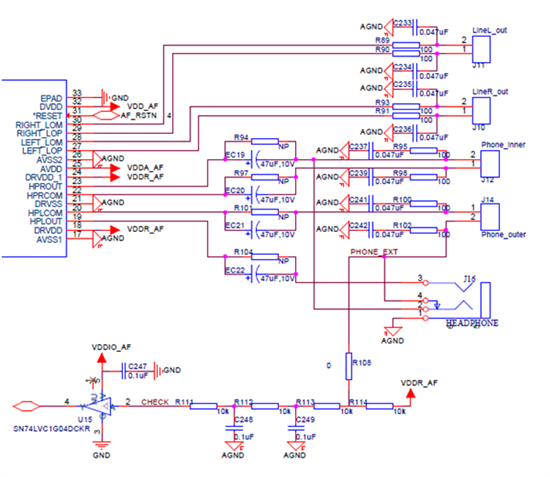

问题1:不知道我所选择的ADC以及DAC输出模式与实际的硬件是否匹配?或是硬件的设计本身就存在问题?我个人觉得这个基于这个硬件平台,我所选取的输入记忆输出模式存在很大问题,但是对照手册,却找不到原因,望能得到大虾的指点!具体的硬件原理图如下:

图2麦克风输入( 我选择MIC2L单端输入,即pin14)

图3 语音输出(我选择pin20、22、23之后的J12和J14输出,即在J12和J14焊接两个小喇叭,但是最终却没有声音。)

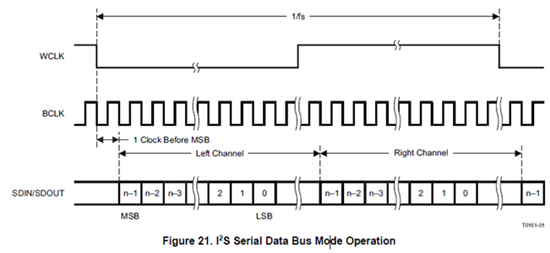

问题2:在整个语音采集的过程中,也就是整个数据的交互过程中,是否可以将AIC3101一直作为主设备?或是AIC3101必须在主从设备之间切换?

问题3:如本例所采用的I2S模式,数据字为长32bit,是否就是将32bit的数据分为左右两个通道各16bit,分别在一个周期的WCLK的高低电平内进行传输?

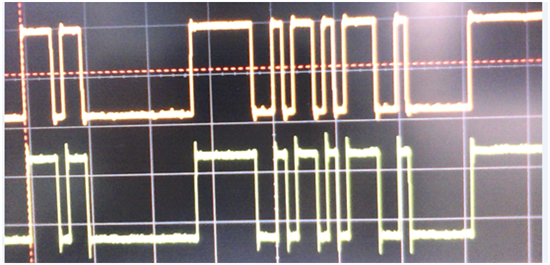

问题4:若问题3的回答是肯定的,图5为AIC3101芯片WCLK(上)与DOUT(下)管脚的波型。不知道DOUT数据是否正确?因为在WCLK的低电平周期内,DOUT的数据显然不止16bit。

图5 AIC3101的 WCLK(上)与DOUT(下)管脚信号

图6 AIC3101的DOUT(上)与DIN(下)管脚信号

最后非常期望能够得到各位大虾的帮助,再次表示感谢!

第一个问题已经解决,果然是输入输出模式选择的问题,现在已经有声音了,但是噪声很大,不知道噪声如何消除,继续等待大虾出现!

你好:

如果是设置的位数是32位,那表示左右的声道的数据位数都是32位。并不是拆开的分别16位。噪声大,估计是你的I2S的信号不匹配所致。

终于等答复了,非常感谢!可是我依然有些不明白:我选择的是I2S,32位的格式,那么在WCLK的半个周期内会有32个BCLK周期,如果说左右的声道的数据位数都是32位,且一个BCLK传输一个数据位,而I2S传输格式的是从第二个BCLK开始传输的,那么在一个WCLK周期内应该是不可能完成左右声道数据的传输的。另外,其他的参数不该变,我只将连续BCLK时钟输出模式改为固定(256bit) BCLK时钟输出,则输出端没有声音。最后,您所说的I2S的信号不匹配会引起噪声大,这个我不是很清楚,我可以从哪方面进行调整?

你好:

你理解的没错。但是这样不会有影响。I2S的协议就是这么规定的。你的输出端没有输出是因为你的BCLK与你的WCLK不匹配。假设你设置的位数为32位,但是你传输的位数却为24位,那么你的数据值就会改变。

再次感谢您的答复!最后非常期待您能给我一些减小或消除噪声的具体方法和建议,谢谢!

你好:

你这个问题太广泛了。噪声来源有很多,从硬件上带来的。比如layout,电源等。

软件上你的配置,包括时钟,I2S的接口等。

多谢您的回复!我再继续调试吧。

如果有噪声,可以分析一下噪声的频谱,分析噪声分布在哪个频段,在codec里设置滤波器把噪声滤掉。

您好:

最近又碰到一些AIC3101的问题。下图是AIC3101datasheet中的第三页:

我现在发现我的芯片在播放声音的时候,DIN和DOUT是有数据的,但是就算是DIN和DOUT没有数据,输出端也是有声音的,也就是说,语音信号在经过PGA后(上图的红点),不过ADC,就直接输出了(上图的红色箭头部分)。现在我是希望能够语音信号只是经过ADC并且通过DOUT输出给CPU进行处理,那么我需要配置哪个寄存器才能把上图中语音信号的红色箭头的通路屏蔽,让信号只经过CPU处理后,再播放?我的ADC等寄存器已经做好相关配置,且是打开的。非常期待能够得到各位的帮助!

问题找到了,是PGA旁路ADC及DAC的原因,还是得再细心一点。。。