两片PCM1792A芯片的同步输出问题

我们在使用PCM1792A这款芯片时,当把两片PCM1792A芯片同步工作时,会差出一个过采样时钟。

具体配置是这样的,比如要配置的刷新率为51.2kHz,过采样时钟设为13.1072MHz,BCK是对这个时钟二分频得到的,这个过采样时钟和BCK都严格比对过,沿和起始位置都是严格对齐的。但是输出的信号会差出一个过采样时钟周期,大约76ns,这个量级的同步误差有点大,而且很有规律,就是随着过采样时钟的变化而变化。

由于对于芯片内部工作不是很了解,所以想请教一下,芯片内部和过采样时钟相关的都有哪些,我们是否能够调整,还是说这款芯片就会存在这样的问题,现在看手册里面有个寄存器DFTH,通过控制这个寄存器能否解决这个问题,或者其他方面,谢谢!

你好:

你这个差一个过采样周期可能是走线的延迟原因。你真的需要输出完全同步吗?因为一般音频信号差一个过采样周期是听不出来的。如果真的要完全同步建议选择哪种集合多个DAC在一起的,例如PCM1681.

这个走线长度是等长的,没有问题,我能接受的误差是20nS以内,我需要同步的数量会比较多,肯定要解决多个DA之间的同步问题,这差一个过采样时钟的问题,很有规律,应该是和内部的哪个结构有关系,望给出建议

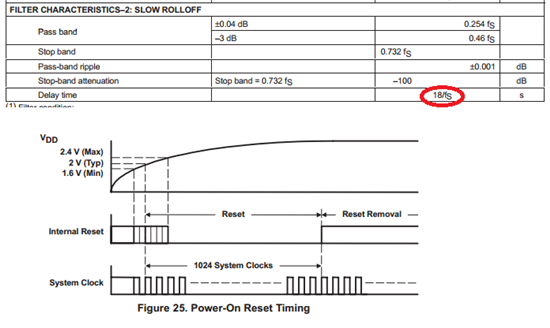

那你输出的数据没有延迟吧?还有就是电源的上电时间。理论上我们芯片的从输入到输出的延迟是一定的,这个跟内部的滤波器,还有上电的时序有关。

你可以测试下每个芯片从有输入到输出的延迟是否一致。

我输出的数据是没有延迟的,电源上电时间是肯定可以保证的,数据给到芯片也是同时的,现在测试的就是数据同时进入芯片,然后输出会差出一个过采样时钟,我想问一下LRCK和SCK这两个时钟的沿关系有没有特殊要求,数据手册中都没有给出这两个的相对关系,因为在192kHz的情况下,128倍的情况下,BCK为了保证大于70nS,这样BCK就要对SCK二分频,会不会在这里有数据沿不是太合适的情况啊

你好:

最完美的情况是BCK与SCK的上升沿对齐。你可以再多试几个芯片看看是不是有同样的问题。

BCK是在SCK的上升沿翻转的,我试了4,5个芯片了,都有这个问题,麻烦你那边能不能给验证一下,是这个芯片本身存在的问题,还是我们这批芯片的问题,谢谢!

你好:

永远是一片比另一片快一个fs么?

做个试验,首先比较第一片和第二片,如果第一片比第2片快一个fs,那么把第2片换掉,换成第三片,比较第一片和第三片,如果还是第一片还是比第三片快一个周期,说明第二片和第三片内部的时间应该是一样的。然后你把第二片换到第一片的位置,比较如果第二片比第三片快或者慢,那就是你板子上的问题。

不是一个fs,是一个sclk系统时钟,而且两个谁快不定

你好:

你的测试输出的地方是在运放之前还是在运放之后?

是在运放后端,我做了一个300多kHz的低通滤波器,不过我电阻用的是0.1%的,电容用的是1%,理论计算时间差最多也就15nS以内,但是现在的情况是查出来一个过采样时钟加这个时间

通过同步复位PCM1792A,可以实现准确同步