TI的D类功放的电源问题

请教TI工程师,TI的D类功放芯片资料了典型电路AVCC,PVCC,AGND,PGND还有GND都是什么关系

你好:

AVCC是模拟电源是给功放内部的模拟电路供电的。PVCC是功率电源是给功放的内部的MOS供电的。AGND是对于AVCC的地,PGND是针对与PVCC的地。

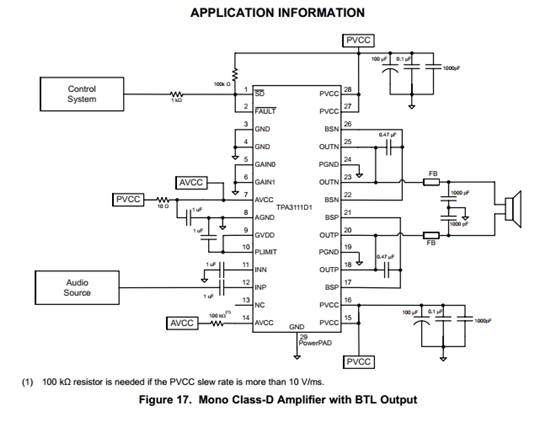

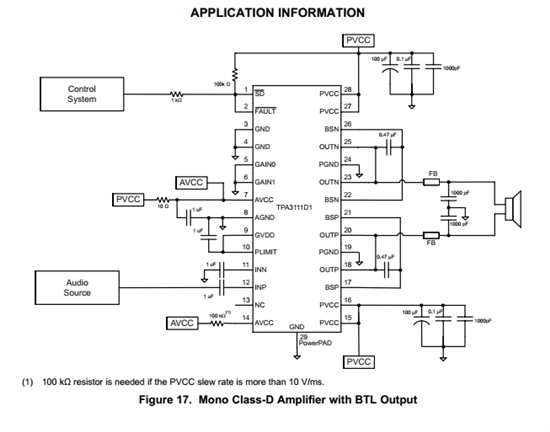

那么这两路电源应该分开接吗,还是能接到一起,就比如下面的TPA3111中的AVCC和PVCC,还有TPA3111的输入就是普通的MP3中的音频信号吗,控制系统接地就行了吧

你好:

可以接到一起。TPA3111的输入是模拟信号,就是一般的歌曲的输入。如果没有MCU,控制信号线可以不接。就是直接把1K那个电阻拿掉就可以了。

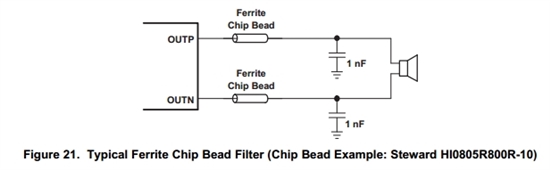

上图的FB环节是什么

这个图的Ferrite Chip Bead又是啥

谢谢Derek Xie这么耐心指导

你好:

FB指的是磁珠。一般D类功放要过EMI 都要加磁珠。如果用了电感就可以不加磁珠。

此芯片在某些条件下可以不使用电感,而用磁珠过EMI。

电感主要为了EMI的因素才考虑使用的了?

那么此功放也就是不需要外部滤波了?

另外power supply有一段文字

the PVCC supply can also be used to power the analog supply(AVCC) and can be used to pull up the logic pins for shutdown (SD) controls,fault detection(FAULT),gain ,and PBTL as long as the voltage slew rate is limited to 10V/ms.

我如何来确定 the voltage slew rate is limited to 10V/ms 也就是电压上升速度,还是说按照demo板 外部滤波电容已经能够确保这一点了?

那这么说就是1脚和2脚接在一起然后和100K的上拉电阻接一块再接VCC

好问题,大神

你好,

你要弄明白Pin1(#SD),Pin2(#FAULT)和Pin14(PBTL)引脚接100kΩ电阻的目的和用途都是什么:

Pin1为芯片关断控制输入引脚,低有效。拉低此引脚芯片Shutdown,拉高此引脚芯片正常工作。

Pin2为芯片错误输出指示引脚,为漏极开路结构,因此要想获得错误信号输出,必须外接上拉电阻。芯片报错时,该引脚输出低电平;无错时输出高电平。

Pin1和Pin2接在一起是实现出错自动恢复功能,当出现短路保护等错误情况时,错误状态会被锁住,清除锁住状态必须将Shutdown引脚置低再置高,因此可以将FAULT引脚和SD引脚短接在一起,出错时FAULT引脚会自动将SD引脚拉低,清除锁住状态后FAULT引脚变高又将SD引脚拉高,芯片正常工作。

Pin14是PBTL和BTL模式选择输入引脚,拉高选择为PBTL模式,该引脚对电压爬升速率有要求,若上拉至PVCC,而PVCC电压爬升速率较快,超过10V/ms时,需要串接100kΩ电阻进行保护,防止损坏该引脚。

PBTL模式是什么,

上图的门驱动是怎么做的,那个加在GVDD下的二极管是自举用的吗?如果只是桥式接负载的话,不需要再加电感滤波吗

你好:

BSP引脚会加一个电容,那个是用来自举来驱动MOS管的,那个二极管是用来防止高电压防止倒灌到GVDD。

PBTL是parallel BTL,相当于把两个BTL并联。

那么Pin7就不同加100k的电阻吗?

自举的话那么门驱动是用光耦做的吗?我们正在做一个同步整流的mosfet的门驱动,不知道怎么驱动,驱动频率只有50HZ不知道行不行

Pin7是模拟电源供电输入端,不需要也不能加100kΩ电阻,加10Ω电阻+1uF电容RC滤波即可。

不要把电平信号输入和电源输入二者搞混了。

pin 7不需要。虽然和PIN14同为电源脚,但是只有5个脚需要限制速率,分别是 SDZ, GAIN0, GAIN1, FAULT, and terminal 14。

这个跟芯片设计有关。

给力