PCM1792A输出噪声问题

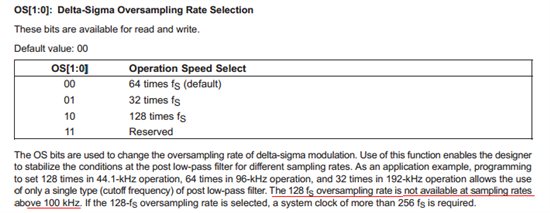

请问PCM1792A在输出时,过采样时钟给24.576M,输出刷新率为192kHz时,过采样倍数为32,BCK是将过采样时钟2分频,在做FFT变换后在噪底上会出现很多毛刺是怎么回事,这直接影响了动态范围;之前我用系统时钟为12.288MHz时,输出刷新率也是设为192kHz,过采样倍数为32,BCK是过采样时钟,但是当时两个通道出现不同步的情况后来看到手册15页中的table1 ,故将过采样时钟提高一倍,以保证128fs,然后将BCK分频以保证周期大于70nS,不过在没有提升频率之前躁底并没有出现毛刺,只是在我将BCK减小到小于70ns的情况下出现了躁底上有毛刺的情况,现在频率提升以后同步问题解决了,但是在各个过采样周期范围内都出现了噪底上有毛刺的情况,我观察了BCK的时钟和之前一样是76ns,保证了大于70ns。具体FFT见附件,我想问的就是如何将这些毛刺去掉,因为在提升频率之前128倍过采样条件下动态范围可以做到113db,现在三个过采样结果一样,都是108db,谢谢!

你好:

你的所有时钟是同时送入的吗?一开始就同步了吗?建议在没有同步前不要power on 芯片,同步后在开始启动芯片。

是同步的,将过采样时钟提升到128fs同步的问题就解决了,不过提升上去之后会有毛刺,现在将频率降下来依然有毛刺

你能试一下等时钟完全同步后在启动芯片,然后看频谱吗?因为这颗料比较老,所以在没有开机的时钟时钟有点问题,就会有很大的噪声,他是以开机的时刻的时钟作为基准时钟的。还有就是你输出的DSDmode,还是PCM mode。DSD mode不支持这么高的过采样时钟。

我说的同步是指BCLK,WCLK等时钟的边沿对齐,当频率过高时,对同步的要求就越高,因为很小的相位偏移可能造成很大的噪声。

请问你说的WCLK是过采样时钟SCLK吗?我的BCK使用SCLK进行二分频获取的,LRCK也是对SCLK根据过采样倍数的4倍进行分频的,可以保证相位;我用的是PCM模式,在启动PCM1792A时,已能保证BCK,SCLK,LRCK的同步性

所谓的边沿对齐是上升沿对齐还是下降沿对齐,还是两个边沿都要保证是对齐的?

这个很重要吗?我能保证在启动DA工作的时候时钟是同步的,之前也是同样的情况是可以保证的,请问BCK和SCLK相位差多少是可接受的范围

6个BCLK以内。还有BCLK和SCLK的相位要固定。对齐当然最好,但是不要每个周期的相位会变化。你的过采样率配置过了吗?

里面有寄存器要配置的

BCK和SCLK相位是稳定的,相位能差出5ns

你查寄存器配置是否正确,比如过采样位数。

这个我设置过了,我又试了几块卡,发现同样的板子,同样的器件,但是出来的效果却差很多,有些器件摘下来重新焊接就会好一些,不过上一批板子和器件出来的性能参数就比较稳定。请问这是什么原因,在生产过程中需要注意什么吗?我们是手贴,然后走的机器

你上一批板子是同样的Layout吗?你可以做个对比,看性能不好的换到性能好的地方看是否能复现。

恩,这两次模拟输出部分Layout没有变,你说同一个通道吗?我这次做了四个板子,每个板子两个通道,这两个通道在不同的板子上性能还不同,物料都是同一批的物料

可能跟你的板子和焊接有关系。

请问IV变换和低通滤波部分的电阻一致性会不会影响噪声

你好:

你的滤波电路的电阻很大吗?这样会带来噪声的。

IV变换处我选用的是680欧姆的电阻,然后有一级放大用的是324和680,接着滤波电路是一比一的,电阻选用的是2k的,这些电阻都是0.1%精度,实际测试好的动态范围可达115dB,差的只能达到106dB,在测试过程中发现增加锡量和更换个别电阻,动态范围会有提升,这个是什么情况啊?

你好:

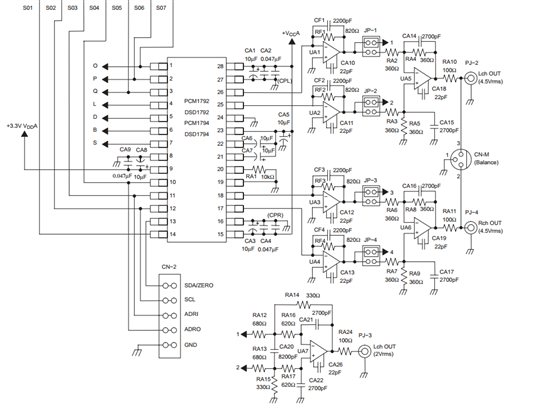

你的原理与是参考我们的EVM板的设计吗?

你可以参考我们的EVM板,你的滤波电阻值太大了。你增加焊锡会减小你的阻抗的。

我是参考这个电路的,滤波器部分用的是差分转单端的电路(下面那个独立出来的电路)这部分电阻用的都是2k的,电容用的是220p和120p,不过有一块动态范围不好的电路板我是通过更换IV变换处的电阻(阻值并没有改变)得到了改善

你好:

你的原理图能看下吗?你改了哪里的电阻?你有测过拿下来的电阻是不是与你焊上去有什么区别?