tas5630驱动容性负载问题

现在我用tas5630驱动容性负载,但是发现经常出现损坏芯片的现象。并不是说工作了很长时间芯片损坏了,而是在有些频率点,一上电就坏掉了。这是为什么,有什么好的解决办法吗?谢谢

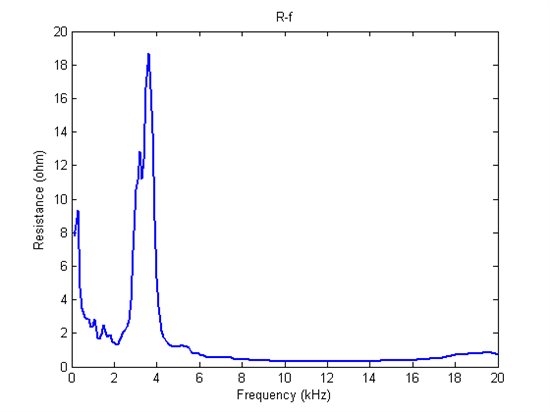

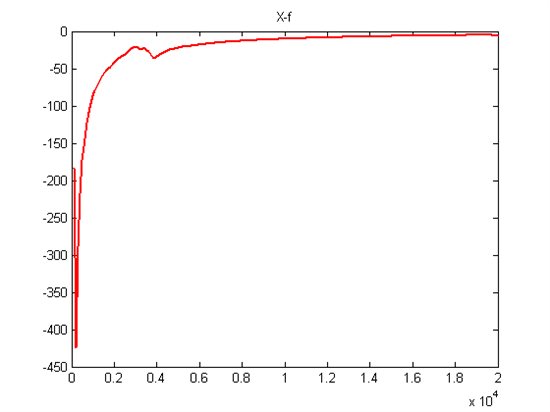

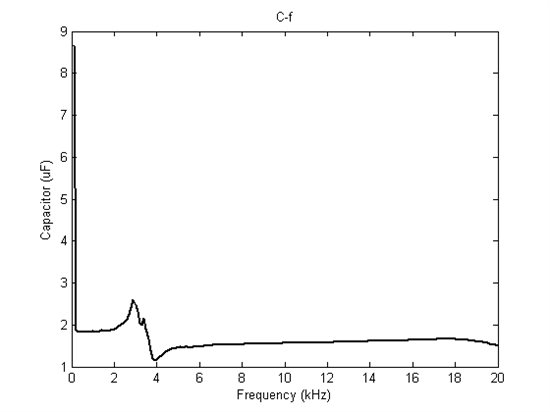

多谢两位的回复,我这里点回复一直没反应,所以我就把负载参数贴到这里了。R-F,X-F分别为负载的阻和抗,C-F是根据抗计算出的电容值。损坏芯片的两个条件是功放的输出幅度大和频率在5kHz以上。而电路泽采用的是ti推荐的 tas5630DKD的评估板电路。

驱动容性负载,能大概描述一下负载情况吗,如大概多大的电容,另外的话,能否给出的电路图,以及你说某些频率点会损坏,能否说明一下具体的几个频率点。

您好,容性负载有多大?能否将原理图发出来看看。

陈先生、Mr flei:

我把负载的特性放到上面了,二位看看,能不能做些补偿的方法减小功放的损坏。

谢谢

首先我不是很了解你的负载时什么,但是从它的负载曲线上看的话,应该是在超过5khz之后,负载的大小已经超过了TAS5630的Rl的范围,请参看datasheet上的page 4上的RL的参数。

能否简述你的应用需求,就需要在多大的频率范围内工作?以及对输出信号有无特殊要求。

flei:

您好,负载是压电片,从手册中所要求的负载范围来说,我们采用的负载确实超了。但是在目前的负载情况下,是否有什么办法来改善一下。

谢谢您!

压电片是低功率因数谐振驱动器件,实际只在几个谐振点工作。因此;做扫频时,采用较低的电压,在谐振附近用高压驱动。驱动时;用并电感来补偿电容电流。这样一来,你的功放就不会过载了。

如果是由谐振引起的,可以考虑增加阻尼/降低Q值。如果Q值很大,在串联谐振频率点,电抗几乎为0。 通过添加电阻或snubber可以改变谐振电路的Q值,来改变谐振时的电抗。

负载阻抗低的时候,降低工作电压,确保开机电流低于过载保护电流,这个芯片18V 是也可以工作, TAS5630开机冲击电流大的时候会烧坏芯片。 也可以控制RESET端,延长软启动时间。