pcm3070-cs k 時鐘疑惑

在Clocks/Interface 的選項卡dividers中問題如下:

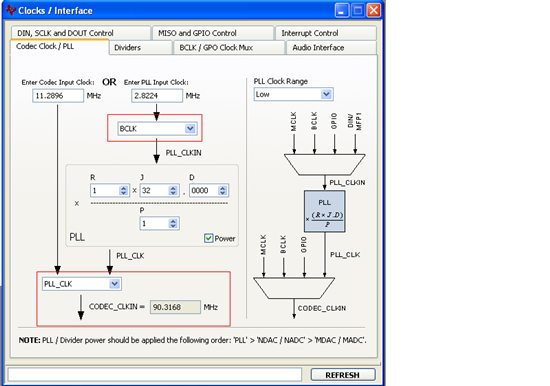

1、NADC/MADC 分別表示什麽意思?不同取值對音頻有什麽影響?

2、DAC_FS / ADC_FS 是不是改變PLL頻率可以改變音頻輸出頻率,達到可以男聲變女聲?

在Codec Clock / PLL問題如下:

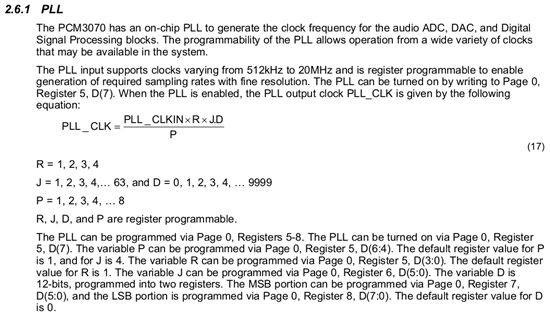

1、R / J / D 分別表示什麽意思?各不同值對音頻影響不同。比如:改變R和J的值,感覺R對音頻的影響比J大。

Hi,

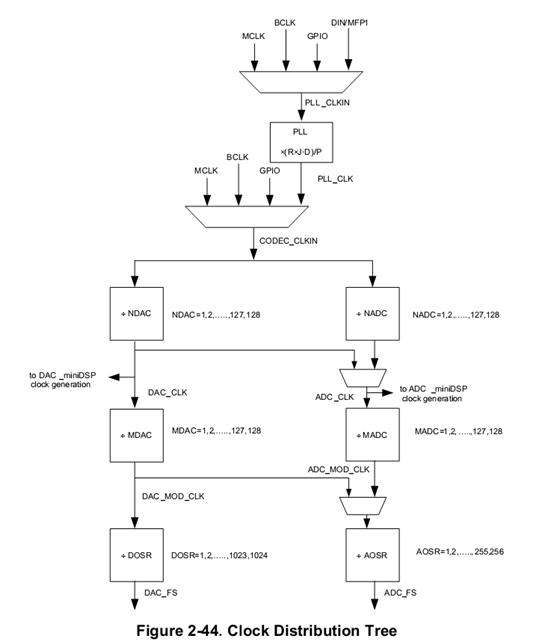

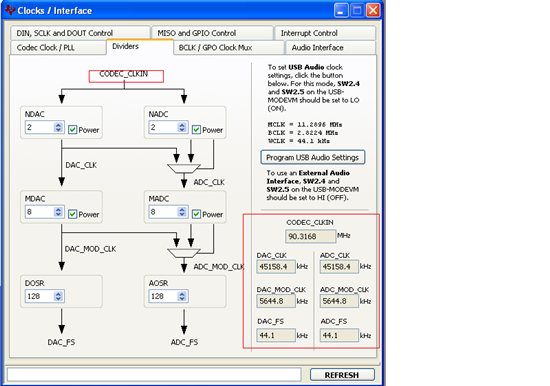

1、NADC、MADC、R、J、D都是用于时钟系统进行分频用的,具体看下图你就明白了:

你可以参考PCM3070 Application Reference Guide :http://www.ti.com/lit/ug/slau332/slau332.pdf了解更多关于时钟配置的信息。

2、改变DAC_FS / ADC_FS 是可以改變音頻輸出頻率,但不能使男声变女声,你可以使用滤波器或一些相关的算法实现,下面有个链接使用Audacity实现你可以参考下:http://audacity.wonderhowto.com/how-to/turn-male-voice-female-voice-with-audacity-424309/

1. 不使用PLL,能获得ADC、DAC及别的数字处理模块所需的时钟信号吗?MCLK怎么控制ADC、DAC所需的时钟信号?

2. 没有MCLK,芯片能正常工作吗?BCLK、WCLK能控制ADC、DAC所需的时钟信号?

Hi

1.不使用PLL可以获得ADC和DAC所需要的数字处理模块所需的时钟信号,但是MCLK必须为Fs的整数倍。比如48Khz的采样率,MCLK为12.288M。44.1Khz的采样率,MCLK为11.2896MHz。MCLK通过Divider分频出ADC和DAC需要的时钟信号。

2.没有MCLK,芯片可以正常工作,但是此时需要用到PLL,设置BCLK为输入的时钟源,配置你们需要的时钟,然后分频PLL产生的时钟得到你们需要的时钟信号。

下面的配置供你参考

还有一个问题:

3254芯片为slave模式,对于I2S接口:输入WCLK=32kHz、输入BCLK=2M、DACDAT和ADCDAT的Word length=16bits,那么BCLK / WCLK=62.5,不等于32(2x16),是不是一定需要:在BCLK节拍作用下,发送32bits所需时间正好等于一个WCLK周期?

谢谢!

Hi,

在Slave模式下,WCLK是由BCLK分频而来的,如果你是16bit数据格式,BCLK=F_WCLK*16*2,分频系数就是16*2。所以在BCLK节拍作用下,发送32bits所需时间自然等于一个WCLK周期。

关于I2S主从配置的一些其他考量,下面资料你可以参考:http://www.ti.com/lit/an/slaa469/slaa469.pdf

你回答的可能不对。我特别强调WCLK=32k、BCLK=2M均为输入,在BCLK作用下,传输16bits,仅用1/4 WCLK周期。之所以考虑BCLK为2M,是因为wordlenth可能为32bits。这样32kHz x 2 x 32 =2 M

Hi,

你的理解是对的,可以这样使用,但要保证BCLK是32kHz x 2 x 32 = 2.048MHz。