FDC2214的IIC地址问题

各位TI 专家好,现想跟您们请教FDC2214的问题,

之前使用FDC1004的IIC能够读取芯片数据,现换成FDC2214同样的IIC模拟IO的程序,却发现芯片不能拉低SDA。我这边FDC221的ADD脚接地,应该是确定地址为0x2A, 我使用模拟IO口去写FDC2214的话,应该是 写 0x54吧, 可就是出现 FDC2214拉低的SDA的情况,芯片 上电 电流30uA。应该焊接正常。其他就是 IIC口接个上拉到单片机IIC接口。目前测试 程序,外部晶振也没有接上应该不影响 芯片IIC工作的啊。

跪求指导。谢谢!在线等,急!

I2C地址没问题,I2C clock占空比还是在变化的?频率多少?

你好! kailyn,

感谢回复, 因为我是IO口模拟I2C接口,所以时钟的占空比不是那么一致,但传输数据的时候的 时钟应该是一致的,大概240kHz吧。

你好! kailyn,

感谢回复, 因为我是IO口模拟I2C接口,所以时钟的占空比不是那么一致,但传输数据的时候的 时钟应该是一致的,大概240kHz吧。

IO 口模拟的I2C,需要看下IO内部是否已经上拉,如果已经上拉,I2C外部则不需要上拉。

你好,

内部没有上拉,采用的外部上拉,同样的电路 同样的程序,只是把地址变化了下,FDC1004 的地址 0x A0, 就下拉SDA, 但是 FDC2214的地址0x54,就不会下拉,两个应该都是I2C接口,怎么FDC2214不工作呢? SD脚 上电拉低的,拉高电流会降低到0.2uA,说明芯片是正常的。其他就I2C的两个脚了。还是没有搞清楚。官方例程里使用的I2C硬件电路。

第九个clock之后data 线就一直为低电平是吗?

datasheet中虽然没有直接给出7bit从机地址,但是根据描述,应该为010101x,然后根据ADDR的高低电平来决定是0X2A还是0X2B,右移一位为0X54和0X56。地址应该是没有问题的。

现在SDA没有拉低,将地址改成0X2A试试呢?

Ox2A也试过了。表示很无奈。该程序也应用过其他好多芯片没有问题。买了demo板回来看是什么问题。

你好,Kailyn

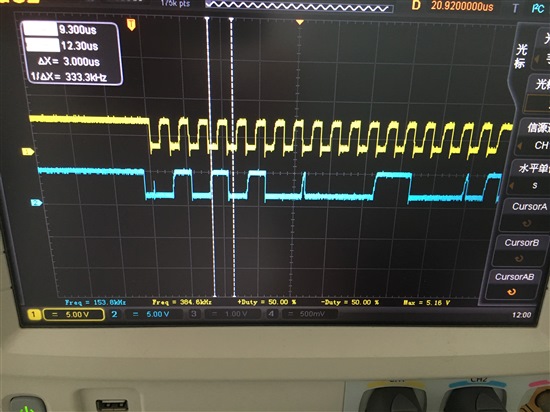

demo板 看波形的话,地址 是没错的0x54。

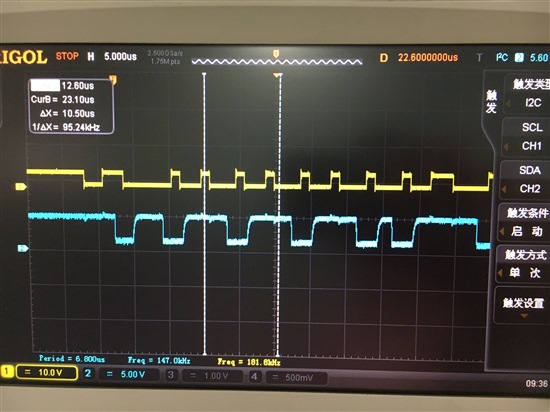

这是我的I2C程序,产生的时序图,接FDC2214。

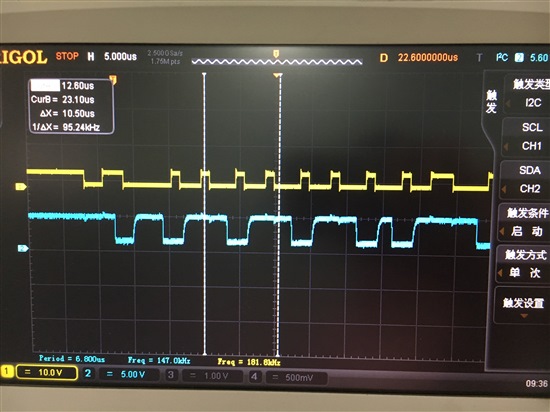

这是同样的程序,FDC1004有拉低。

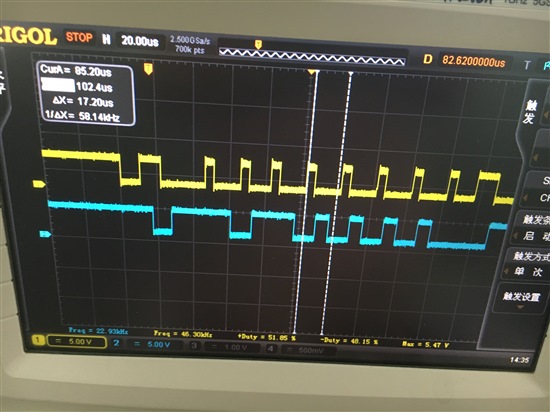

这是demo板上的FDC2214程序。。

我的clk频率60kHz, demo的 是靠近400kHz,其他地址没啥问题。

关键的clk信号数据都没差,搞不清楚为什么2214没拉低。还请指教。麻烦了。

确认下第九个clock之后data 波形一直为低吧?I2C的上拉电阻取值多大? 4.7Kohm?