SN74LS123使用问题

时间:10-02

整理:3721RD

点击:

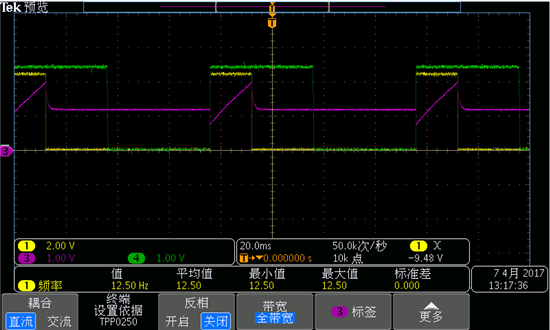

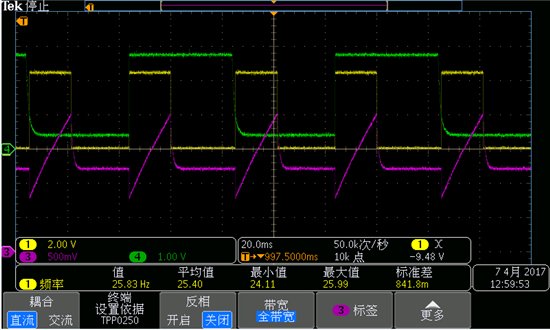

CH1:芯片13脚输出波形 CH3:15脚波形 CH4:2脚输入波形

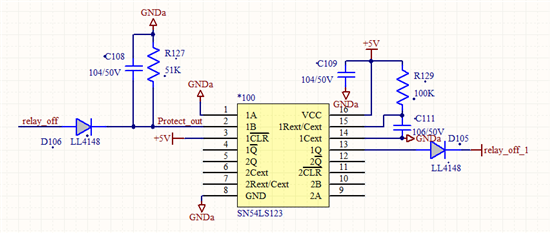

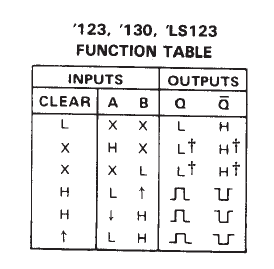

用74LS123想做一个单稳态触发电路,但目前发现一个问题,根据真值表,按照原理图中的接法,检测芯片2脚的上升沿,随后13脚输出个固定脉宽的波形。

第一张波形图为去掉原理图中D106、C108、R127时,输入信号直接接入2脚,检测上升沿触发

第二张为输入信号接relay_off时,发现上升沿、下降沿都触发。这是为何?肯定大神解答!

跪求大神解答啊!

是用面包板测试的吗?如果有noise,不管是来自VCC还是来自GND都会造成边沿误触发。

是用面包板测试,但这样能不能说明在实际PCB上时,也会出现受干扰误触发的现象,导致产品功能不可靠。另对于单稳态触发器,有没有要求触发脉冲宽度一定要小于单稳态时间宽度 ,或者小于的话,不会出现上述误触发情况

你用示波器测一下第二种情况下,芯片输入脚上的波形怎么样?输入高电平容易理解,输入低电平的时候,理论上对于芯片输入脚是没有作用的,因为二极管隔离了。