DRV8432,在CBC模式下,FAULT引脚一直是LOW,求解答,多谢!

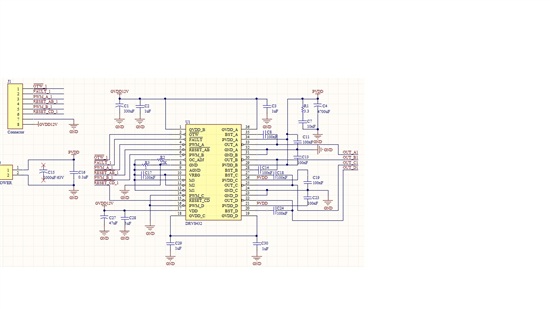

感谢大家的帮助,DRV8432,工作在010、CBC模式,GVDD供电12V正常,PVDD供电15V正常,FAULT引脚是low,otw是high,datasheet上说这是过流或者欠压,供电信号检查了没问题,欠压排除,负载接100欧姆电阻,测了没有电流,为高阻状态,检查各引脚无短路,VREG3.3v正常,小弟实在弄不明白了,请大家帮我看看,感激不尽!

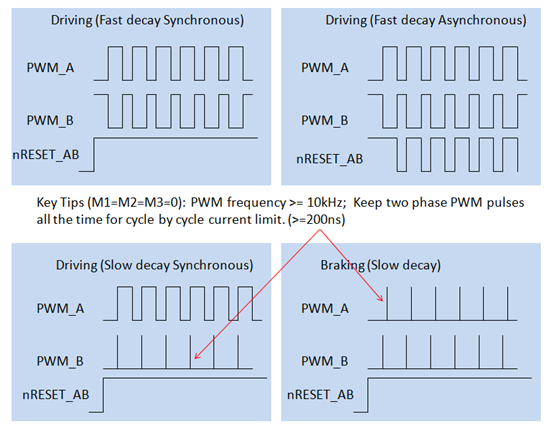

请问输入端信号PWM_A_1,PWM_B1_1是怎么样子?DRV8432采用自举的方式,占空比无法达到100%,输入必须为PWM信号

暂时只用了PWM_A,输入10kHz,50%PWM信号,然后FAULT一直是low啊

目前只采用PWM_A一路,输入10KHz,50%的PWM信号,PWM_B无输入。按照DRV8432 POWER UP 的步骤操作,FAULT还是low.

您好,请参考上面的图,所有的PWM_x都要加入信号,0%或100%都应该避免,这CBC模式才可持续。

同时,VM端必须保证大电容的存在(>100u 根据电流来,电流越大,电容也要加大),0.1u只能做为辅助高频旁路,它的容值太小,无法保证PWM电流抽取时电源引脚的稳定性,可能会出现反复的瞬态UVLO错误。

从你贴的原理图上看来,你的GVDD_C 和GVDD_D没接到电源吗? 只有GVDD_A和GVVD_B接到GVDD12V?

你好,感谢您的帮助,我用的010模式,现在两路信号都加了,并且fault和ote都是high,说明正常工作。但是,我在OUT_A和OUT_B后分别接了100Ω的电阻,但是测不到输出,这是怎么回事呢,按理说,应该是放大后的PWM波才对啊?多谢回答!

你好,GVDD_C和GVDD_D的确没有接到电源,现在飞线了,ault和otw都是high,说明正常工作。但是,我在OUT_A和OUT_B后分别接了100Ω的电阻,但是测不到输出,这是怎么回事呢,按理说,应该是放大后的PWM波才对啊?多谢回答!

你好,你的电路设计中设置了M1:M2:M3=010,所以是并联输出模式,OUTA和OUTB是输出并联起来做为一路用的,请参考datasheet中的Figure 9 进行电路设计。

你好,按照figure9连接后,能够勉强输出PWM波,但是干扰好大啊

你好,你说的干扰应该只是因为线路上接了电感,所以示波器接到电阻端上看到可能有类似于振铃的波形,如果你接在电感之前,也就是OUT_A和OUT_B脚,应该是干净的PWM波形

好的 十分感谢!

VM端在哪呢?