LVDS和CLC012均衡速率问题

硬件设计LVDS之间用CLC001驱动器和CLC012均衡器,工作后CLC012接收的1023发过来的10位数位同步码即0F,时钟15M,发现012有输入没有输出。LOS信号拉高。后来换了014发现又可以工作了。查阅资料发现两者没有明显的区别。后来将发送数据改为F0后012就工作了,总结问题可能是出现在012均衡的速率问题上,就自己理解的用15M时钟,理论上1023的速率应为15乘以12位的值,可实际传输过程中,一个时钟内数据只有1-0一次变化,实际的有效速率为15乘以2为30Mbps,将数据改为F0后将其速率从30提高到60,符合012工作速率50-650Mbps,不知道是不是这样理解的012工作速率?其二,若是这样理解那么为什么014在30Mbps却能工作?

描述好混乱,能不能配个图,分步说明?

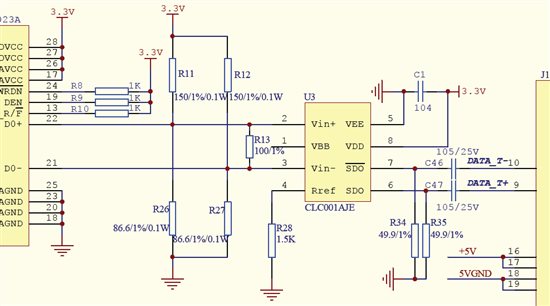

发送原理图

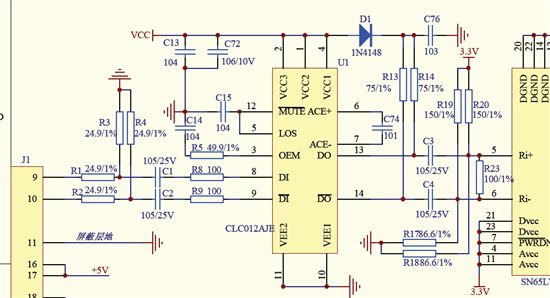

接收原理图

硬件连接:

(1)CLC001和CLC012两者之间用的是3米的屏蔽双绞线

(2)发送端:SN65LV1023A 后接电缆驱动器CLC001;接收端:CLC012后接SN65LV1224B;SN65LV1023A和SN65LV1224B时钟采用14.7456MHZ

问题描述:

上电后SN65LV1023A 一直发送同步码0000011111,发现CLC012有输入信号(8和9引脚)没有输出信号(13和14引脚),并且输入信号因为只经过3米双绞线传输衰减很少;将发送数据改为1111100000后,CLC012大概过4S左右后有输出;将数据改为1010101010后,CLC012上电就有输出信号。

问题:

(1)个人理解这和CLC012工作速率有关系,问题是CLC012的数据传输率为50Mbps~650Mbps的计算方法是不是14.7456MHZ乘以12位(SN65LV1023A的终止位和起始位各一位),还是理解为和发送数据的高低变化次数有关?

(2)将CLC012芯片换为CLC014芯片SN65LV1023A 仍然发送同步码0000011111,发送立即有输出信号,经过多次测试很稳定。两者速率相同,为什么CLC012芯片工作时出现这个问题?

TI工程师,您好,我已经将图贴上去了,并详细描述了现象,您能看看到底是不是速率问题?麻烦了

012和014没看到速率上的区别,我把你这个问题转给了对应的产品线,等我问下他们。

好的,麻烦您了

您好,关于LVDS和均衡器的速率传输问题,您能帮我联系下懂的TI工程师吗?麻烦了,测试想确定下问题究竟出哪了,不胜感激!

已经问了。因为芯片比较老,比较难找到以前的人。

另外放圣诞节,稍等等,不管有没有消息,我都会告诉你的。

数据传输速率data rate 的定义为bps,bit per second,指的是传输每一个bit数据的时间,如果时钟是14.7456MHZ的话,那么传输速率为14.7456MHZ乘以12位是正确的。

关于你提到的同步问题,我看了下你的电路图,数据间采用的是交流耦合的连接方式,在这种高速数据传输当中,交流耦合的话,在连续发送0或者1的时候虽然0和1的数目相同打到了直流平衡,但是容易丢码现象,所以当你改成01010101这种间隔方式发送的时候便没有这个问题,或者建议你将电容去掉改成直流耦合连接的方式看看。

直流耦合方式已经试过了,均衡器仍然不工作。

另外问题的重点是用交流耦合测试的结果:均衡器输入信号很好,没有丢码现象,但它就是在发送0F时没输出,改为F0就有输出了,但上电后均衡器工作的时间不定;若是数据采用0/1变化比较多的,它上电就工作。

所以,我想确定下是不是012的工作频率问题?其次,发送同步码时,将clc012换位clc014后,014就有输出,所以是不是014性能上对信号的频率要求没有012那么苛刻?

还有一个问题啊,CLC012这款是5V供电的啊,你电路图中是3.3V供电,CLC012输出上拉75ohm到5V,这样的话如果和3.3v系统接的话还会出现IO口间电平不匹配的情况

刚刚发现,CLC012,CLC014都是已经停产的产品了,不建议使用了,建议你使用LMH0074这款来代替,3.3V供电的,data rate为125 ~ 540 Mbps。 你可参考下这篇应用文档:

http://www.ti.com/lit/an/snla124a/snla124a.pdf