SN54LVTH162245使用问题求助

时间:10-02

整理:3721RD

点击:

目前在使用SN54LVTH162245做接口电平转换,设计时把#OE直接拉低到地上,#DIR加上拉电阻连接到控制信号,想通过控制#DIR来实现传输方向控制。实际上电后发现接口都被拉在高电平3.3V了,不太清楚为什么。怀疑把#OE直接拉死到低有关,但不太确定,看看大家有没有了解的。谢谢。

这个跟OE关系不大。OE只控制输出使能。能否给一下你的电路?看样子,是被置高电平了。

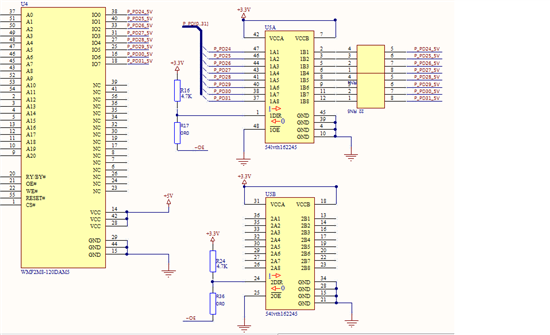

电路是这样的。

电路是这样的。

我将直连到地上拉低的#OE跳掉,采用低电平有效控制信号加上拉电阻进行连接后,这个问题被解决了。但是还是不太明白问题出在哪里。

datasheet中有这么一句话:When VCC is between 0 and 1.5 V, the devices are in the high-impedance state during power up or power down.

However, to ensure the high-impedance state above 1.5 V, OE should be tied to VCC through a pullup resistor。也就是说在上电或掉电时,在0~1.5V之间是处于高阻抗状态的,为了使得当大于1.5V时,器件仍处于高阻抗状态,需要将OE上拉,并且需要注意的是这款芯片内部集成了总线保持电路,也就说无效的输入也会使得其处于一个有效的逻辑电平,所以当OE为低时,器件本身处于一个有效的逻辑高的状态,所以当你将OE上拉之后,处于高阻抗的状态了。 如果这款器件内部没有集成总线保持电路的话,直接将OE拉低是没有问题的。

我也注意到这个地方的描述了。应该是这个问题。十分感谢