DS90UB925的back channel传输速率问题

hi!TI工程师:

我的应用是:FPGA1—>926—>925—>FPGA2,利用back channel由FPGA1发送数据给FPGA2。通过配置寄存器,我让926的GPIO为输入,926的GPIO为输出,测得每个925上的GPIO数据传输速率最高为170k左右。

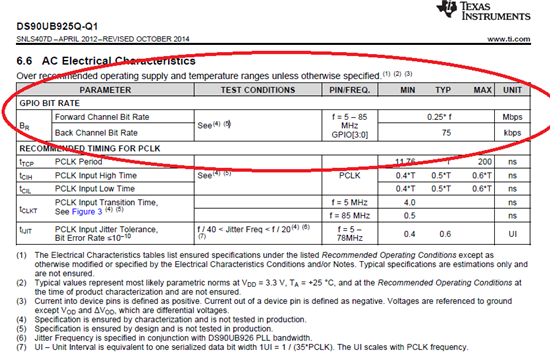

问题1:关于GPIO的传输速率手册上并没找到相关介绍,我想知道该速率最高能跑到多少,需要配置什么寄存器吗?还是GPIO速率是固定的?

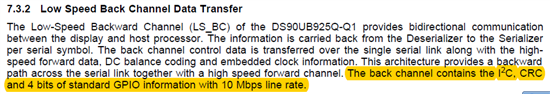

问题2:如图,最后一句话的10M rate是怎么得到的?谢谢

对于这两款serdes来说,back channel的data rate是固定的,为10Mbps。

有些serdes,back channel的data rate可以是5Mbps,10Mbps或者20Mbps,是通过寄存器来配置的,比如DS90Ux94x。

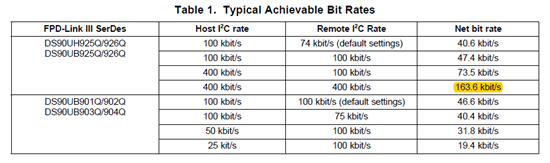

hi,TI工程师:1、我想知道10Mbps data rate是怎么得出来的?其中i2c如图最高为163.6kbit/s,我测的每个GPIOpin速率可以支持到170k左右。

2、另外请问您有什么测试关于GPIO速率的方法 以及 您所了解的back channel方向的GPIO速率一般是多少?

您的这个图是针对哪款芯片的?我在925的datasheet中没有看到呢。

datasheet中10Mbps的理解很简单,指的是low speed Back Channel Data Transfer, 而PCLK的频率范围为5MHz~85Mhz,因此在低速5MHz时,back channel data rate=2*5MHz=10Mbps。 这里的2代表的是一个clock有两位data,高和低。

hi! Kailyn,您好!

1、楼上的iic频率的图片摘自snla131a文档,是针对ds90ub925/926芯片的。

2、请问有没有关于925/926的GPIO的相关资料,我还是想知道官方的关于GPIO back channel的速率的描述

谢谢!

在datasheet中有列出GPIO典型速率了。在下面注释中可以看到,这个在量产中没有实际测试,只是spec 的值。