DS90UB913Q+DS90UB914Q 时钟问题

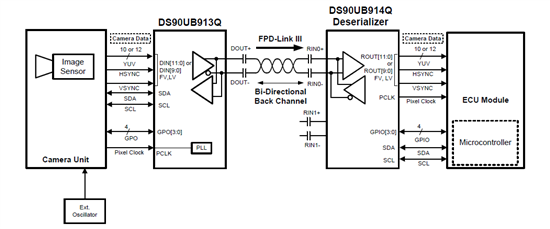

应用方式:AR0230+ DS90UB913Q+DS90UB914Q+HOST

参照如下方式搭建

SENSOR输出PCLK:74.25MHZ +12BIT

目前问题

SENSOR输出数据 PCLK:74.25MHZ VSYNC:30HZ HSYNC::32.56KHZ 已经送入913芯片(已确认送入)

914输出数据:PCLK:55.68MHZ VSYNC:4-8MHZ(不是固定值不停变动) HSYNC:4-8MHZ(不是固定值不停变动)

不知道914输出数据为何不正常?

先确认两点:

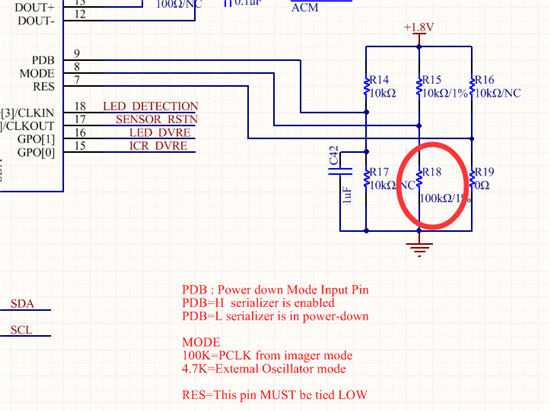

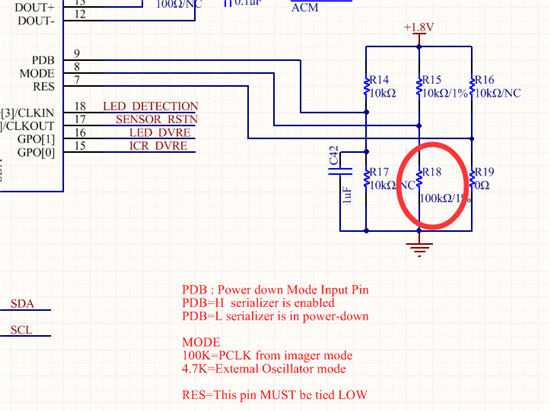

1: PCLK来源于camera,那么Rmode电阻值100Kohm是否有接?

2. BIST自检测试有没有做?先建议测试BIST看是否pass。

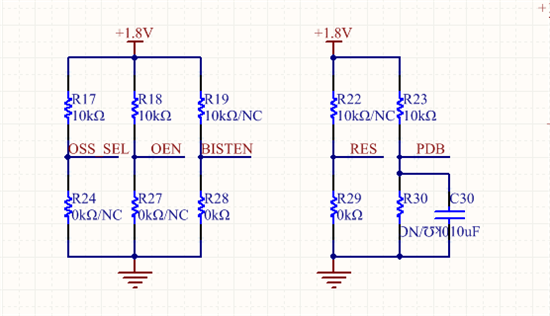

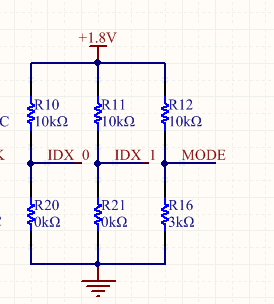

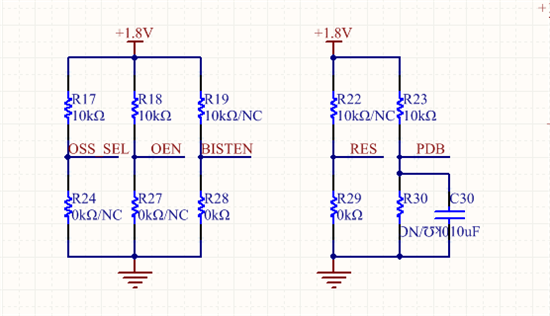

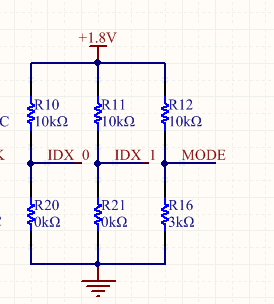

1. DS90UB914Q配置电阻NC为空; MODE 配置下接电阻3K(分压处电压0.41V)。

DS90UB913Q配置电阻如下。RMODE下拉100K(分压电阻处电压1.6V)

2. BIST内置自检

配置

BISTEN=H(1.8V)

GPIO0=L

GPIO1=H

状态

PASS=H用示波器测试结果为高电平,无出现其它波形或干扰情况。

LOCK=H

断开913连接后,

PASS=L

LOCK=L

1. DS90UB914Q配置电阻NC为空; MODE 配置下接电阻3K(分压处电压0.41V)。

DS90UB913Q配置电阻如下。RMODE下拉100K(分压电阻处电压1.6V)

2. BIST内置自检

配置

BISTEN=H(1.8V)

GPIO0=L

GPIO1=H

状态

PASS=H用示波器测试结果为高电平,无出现其它波形或干扰情况。

LOCK=H

断开913连接后,

PASS=L

LOCK=L

恩 BIST没问题。说明整个链路是没问题的。

有没有尝试PCLK改成使用外部时钟验证下?我怕内部时钟输出jitter的影响,造成整个链路抖动比较大造成接收端输出有误差。

发现个有规律的现象:

送入913的PCLK频率是914输出的频率的4/3倍,例如913 PCLK为74.25MHZ 914 PCLK为55.68MHZ ,感觉像是寄存器设置中分频问题

修改硬件周期太长,这个无法验证

您好!

建议您修改913、914中BIST内部寄存器来清除内部时钟和外部时钟重叠的问题,这样就不需要修改硬件就可以disable内部时钟。

方法:1.在寄存器中使能BIST override功能,即使能BIST内部寄存器控制

2.disable BIST 功能

3.选择BIST时钟来自外部。