SN65DSI84 进行MIPI转LVDS点液晶屏概率性黑屏--急

采用SN65DSI84 进行MIPI转LVDS点液晶屏遇到了黑屏的问题,急需解决,

现象:

1、重复开关机会存在一定概率(1%~5%)的液晶屏黑屏现象,每一块板子都有此现象;

2、此时LVDS通道输出 A_Y2,A_CLK,B_Y2,B_CLK 均有信号,但 A_Y0,A_Y1,A_Y3,B_Y0,B_Y1,B_Y3 均无信号;

3、黑屏后,SN65DSI84重新执行一遍初始化流程(不动MIPI信号)液晶屏显示正常;

4、只要液晶屏显示正常了,就不会再黑屏;

5、黑屏后,读取0XE5寄存器为0X01,重复读取0~30分钟,0XE5寄存器值可能会出现不为0X01(DSI报错)。

麻烦分析问题所在,多谢了!

你好,

请用高速示波器测量一下输入信号的抖动,眼图是否合格,各并行信号间的skew是否符合要求, 电缆及连接器的质量是否达标,DSI84的供电噪声是否正常。 总之,我比较怀疑是输入信号质量不好造成黑屏。

你好,

目前缺少高速示波器测量,MIPI信号源与DSI84芯片在同一块PCB板上,信号输入线都有进行100欧姆差分阻抗控制,参考地平面完整,PCB布线方面可以说是不存在问题,供电采用LDO,纹波噪声在20mV以下。不理解的是不管黑屏还是正常,0xe5寄存器读值均为0x01(PLL_ULOCK),如何才能实现读值为0x00?黑屏时,0xe5读值出现其它数值也是一个较小的概率,如果是DSI信号问题,为何0xe5寄存器报错基本上是不准的?

你好,

由于黑屏不是每次都出现,所以e5寄存器也不是每次都报错。报错的时候已经是比较严重的问题了,加之报错时信号出问题只是在DSI84本身及其前端,此信号传输到屏上时信号质量会更差,造成屏端解码芯片更加无法解码,所以黑屏。 就像你说的,信号质量跟PCB布局有关,但跟MIPI信号源的质量也有很大关系,比如MIPI源的时钟不干净,电源不干净,或者其他信号干扰,都会造成信号抖动过大而造成e5报错。 因此我还是建议你检查信号源的抖动情况,并实际测量给DSI84的供电已经MIPI信号源芯片的供电以及时钟抖动,不然我们用其他方式更加难以定位问题。

还有一半办法来验证是不是信号质量的问题:请把分辨率降低,看是否还黑屏,如果不黑了,说明是信号质量问题,原因是低分辨率对信号噪声的容忍度会显著增强

你好!

问一下,这个问题解决了吗?

我们也遇到了同样的现象:重复开关机会导致黑屏;所有板子都会有此现象。

重新开机或者重新初始化,屏显示恢复正常。

能够排除硬件和设置参数问题。

怀疑是初始化流程有问题,但不知道哪里有问题。

经过试验,基本解决了反复开关机概率性黑屏的问题。目前试验了上万次,未再发现SN65DSI84初始化失败的问题。原因确实是由于程序初始化流程问题,须严格遵守datasheet中描述步骤。证明了硬件设计,包括PCB是没有问题的。SN65DSI84对PCB布线的要求也没有传说的那么“高”。我们先后设计制作了三种MIPI->LVDS方案,TI的方案除了调试困难,其性能和转换后的图像质量确实无可挑剔。有点儿小贵。

请问,你们使用sn65dsi84这颗IC调试的分辨率是1920x1080的吗?

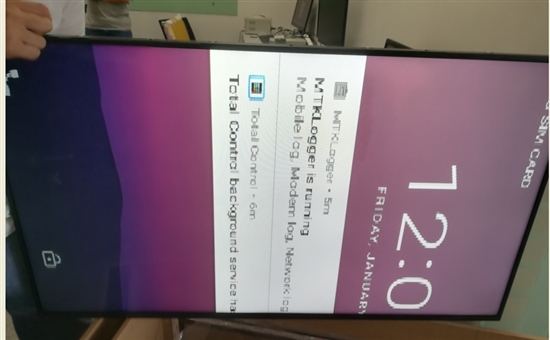

我们遇到如下问题,出来图像显示不完整,有哪位知道是什么原因吗?

是的,输出是1920x1080。

从图片看,你的MIPI输出需改成横屏输出。有个别手机芯片,把横屏输出的功能“锁”了,只能竖屏输出。

你好:

能否共享一下你的驱动,我的已经2个多月了,还是没有点亮,非常感谢!

以下是1080p屏上用过的一组配置,你根据自己的屏改一下FP/BP/SYNC值后试试!

ret = sn65dsi83_regw(i2c, 0x09, 0x01);

if(ret < 0)

return;

//PLL_EN(bit 0) - Enable LAST after addr 0A and 0B configured

sn65dsi83_regw(i2c, 0x0D, 0x00);

msleep(10);

//HS_CLK_SRC bit0

//LVDS_CLK_Range bit 3:1

// sn65dsi83_regw(i2c, 0x0A, 0x04);

//DSI_CLK_divIDER bit7:3

//RefCLK multiplier(bit1:0)

//00 - LVDSclk=source clk, 01 - x2, 10 -x3, 11 - x4

// sn65dsi83_regw(i2c, 0x0B, 0x00);

//DSI Ch Confg Left_Right Pixels(bit7 - 0 for A ODD, B EVEN, 1 for the other config)

//DSI Ch Mode(bit6:5) 00 - Dual, 01 - single, 10 - two single

//SOT_ERR_TOL_DIS(bit0)

sn65dsi83_regw(i2c, 0x10, 0x26); //use 4 lanes DSI

// sn65dsi83_regw(i2c, 0x11, 0x00);

sn65dsi83_regw(i2c, 0x12, 0x57); //DSI CLK 411MHz

// sn65dsi83_regw(i2c, 0x13, 0x00);

//bit7: DE_Pol, bit6:HS_Pol, bit5:VS_Pol, bit4: LVDS Link Cfg, bit3:CHA 24bpp, bit2: CHB 24bpp,

//bit1: CHA 24bpp fmt1, bit0: CHB 24bpp fmt1

sn65dsi83_regw(i2c, 0x18, 0x6C); //use 4 lanes LVDS

sn65dsi83_regw(i2c, 0x19, 0x0F);

sn65dsi83_regw(i2c, 0x1A, 0x03);

// sn65dsi83_regw(i2c, 0x1B, 0x00);

//CHA_LINE_LENGTH_LOW 1280

sn65dsi83_regw(i2c, 0x20, 0x80);

//CHA_LINE_LENGTH_HIGH

sn65dsi83_regw(i2c, 0x21, 0x07);

//CHA_VERTICAL_DISPLAY_SIZE_LOW 720

// sn65dsi83_regw(i2c, 0x22, 0x00);

// sn65dsi83_regw(i2c, 0x23, 0x00);

// sn65dsi83_regw(i2c, 0x24, 0x00);

//CHA_VERTICAL_DISPLAY_SIZE_HIGH

// sn65dsi83_regw(i2c, 0x25, 0x00);

// sn65dsi83_regw(i2c, 0x26, 0x00);

// sn65dsi83_regw(i2c, 0x27, 0x00);

//CHA_SYNC_DELAY_LOW

sn65dsi83_regw(i2c, 0x28, 0x20);

//CHA_SYNC_DELAY_HIGH

// sn65dsi83_regw(i2c, 0x29, 0x00);

// sn65dsi83_regw(i2c, 0x2A, 0x00);

// sn65dsi83_regw(i2c, 0x2B, 0x00);

//CHA_HSYNC_PULSE_WIDTH_LOW

sn65dsi83_regw(i2c, 0x2C, 0x04);

//CHA_HSYNC_PULSE_WIDTH_HIGH

sn65dsi83_regw(i2c, 0x2D, 0x00);

// sn65dsi83_regw(i2c, 0x2E, 0x00);

// sn65dsi83_regw(i2c, 0x2F, 0x00);

//CHA_VSYNC_PULSE_WIDTH_LOW

sn65dsi83_regw(i2c, 0x30, 0x04);

//CHA_VSYNC_PULSE_WIDTH_HIGH

sn65dsi83_regw(i2c, 0x31, 0x00);

// sn65dsi83_regw(i2c, 0x32, 0x00);

// sn65dsi83_regw(i2c, 0x33, 0x00);

//CHA_HOR_BACK_PORCH

sn65dsi83_regw(i2c, 0x34, 0x82);

// sn65dsi83_regw(i2c, 0x35, 0x00);

//CHA_VER_BACK_PORCH

// sn65dsi83_regw(i2c, 0x36, 0x00);

// sn65dsi83_regw(i2c, 0x37, 0x00);

//CHA_HOR_FRONT_PORCH

// sn65dsi83_regw(i2c, 0x38, 0x00);

// sn65dsi83_regw(i2c, 0x39, 0x00);

//CHA_VER_FRONT_PORCH

// sn65dsi83_regw(i2c, 0x3A, 0x00);

// sn65dsi83_regw(i2c, 0x3B, 0x00);

sn65dsi83_regw(i2c, 0x0A, 0x05);

sn65dsi83_regw(i2c, 0x0B, 0x28);

sn65dsi83_regw(i2c, 0xE0, 0x01);

//Clear all error code

sn65dsi83_regw(i2c, 0xE5, 0xFF);

//PLL_EN(bit 0) - Enable LAST after addr 0A and 0B configured

sn65dsi83_regw(i2c, 0x0D, 0x01);

msleep(10);

//SOFTRESET

sn65dsi83_regw(i2c, 0x09, 0x00);