DP83822与TMS320C6748接口设计

时间:10-02

整理:3721RD

点击:

您好,

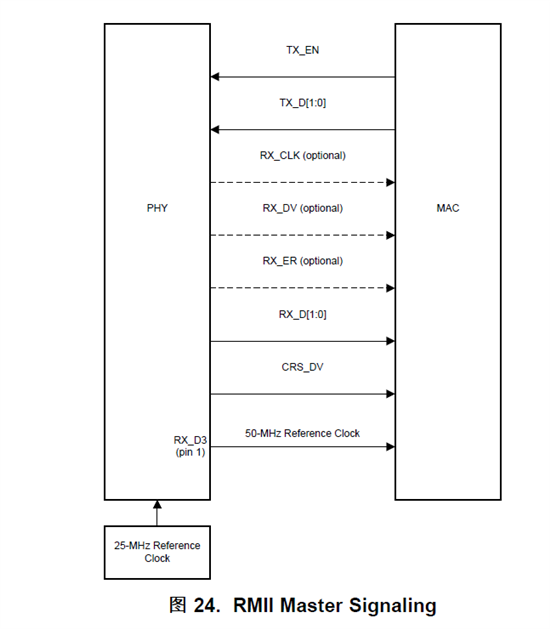

设计C6748与DP83822接口,框图参考DP83822数据手册,MAC端采用C6748,PHY采用83822,接口采用RMII Master Signaling形式,其中50MHz-REFER Clock通过DP83822的RX_D3(PIN1脚)输出给C6748,主时钟采用25MHz Crystal时钟,上述设计有什么问题?

谢谢,

没有问题,RMII mode的话,参考时钟可以是25MHz的crystal接到XI,XO,也可以是25Mhz有源晶振。

并且如果是通过hardware bootstrap 配置RMII master mode的话,自动默认的是RX_D3 为50Mhz 输出。

谢谢,

Kailyn Chen

没有问题,RMII mode的话,参考时钟可以是25MHz的crystal接到XI,XO,也可以是25Mhz有源晶振。

并??如果是通过hardware bootstrap 配置RMII master mode的话,自动默认的是RX_D3 为50Mhz 输出。

一定要有源晶振吗?无源晶振可以不?