SN74LVC1G74设计的开机电路状态翻转问题

时间:10-02

整理:3721RD

点击:

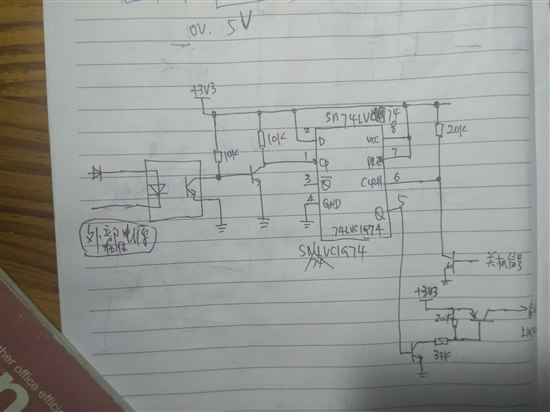

如上图,选择SN74LVC1G74作为一个启动电路,要求外部电源出现的时候,CP输入引脚有一个上升沿,使Q输出高电平。这个功能能够实现。

现在存在一个问题:

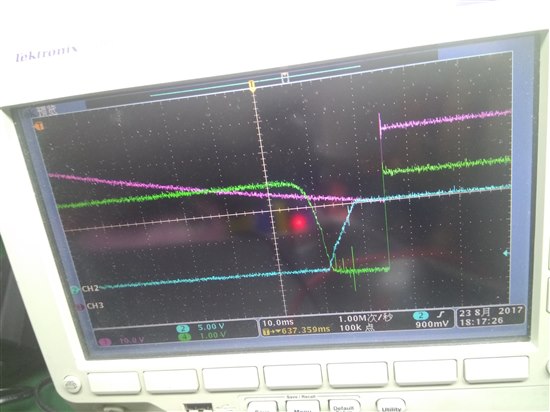

1、关机信号出现以后,Q输出低电平,辅助电源EN脚为低,辅助电源关闭,系统供电的12V(下图中青色曲线)输出为0V,关机成功;这个时候希望系统保持关机状态不变,即使外部在位的信号撤除,也要保持系统处于关机状态。

2、辅助电源关闭后,若此时(外部电源在位消失,粉色曲线逐渐下降)光耦停止导通,CP引脚信号(下图中绿色曲线)从3.3V逐渐下降到0V;

3、此刻CLK信号为低,按照SN74LVC1G74的真值表,Q输出Q0,也就是维持上一个时刻的低电平不变。

4、但是,Q输出了高电平,拉高了辅助电源的EN脚,触发了辅助电源芯片,产生了12V系统电压(下图中青色曲线);

现在的疑问是,为什么CP信号为L时,产生了触发信号?

示波器抓了一下,下降过程中,在1.4V左右脉冲有抖动,无意中造成了一个上升沿,所以产生了启动信号。

问题解决了就好,那在1.4V左右是怎么造成的脉冲抖动呢?clock是如何提供的。

在CP信号之前增加一个施密特触发器(整形电路)之后,此电路工作正常。

CP的产生:外部电源驱动光耦导通,经过MOS和施密特电路整形,产生一个上升沿,此上升沿CP信号会把D(此刻为1)输出到Q,进而产生辅助电源的启动信号(EN为1)。