新开发的单板上使用了两片Retimer,型号:DS125DF1610,有两个问题咨询下

问题一:在Retimer的输入、输出都有P、N的交换,请问可以配置哪个寄存器来改变对应的channel。是修改FIR的main、pre、post参数?

问题二:为了走线方便,我们需要在Retimer做内部逻辑交叉,比如输入1B交叉到输出1A、输入1A交叉到输出1B,寄存器该怎么配置?

问题一:在Retimer的输入、输出都有P、N的交换,请问可以配置哪个寄存器来改变对应的channel。是修改FIR的main、pre、post参数?

A: 是的,如果输出driver极性相反,可通过修改这三个参数。

问题二:为了走线方便,我们需要在Retimer做内部逻辑交叉,比如输入1B交叉到输出1A、输入1A交叉到输出1B,寄存器该怎么配置?

A: 建议参考datasheet中7.3.4 Cross Point Switch的介绍,需要修改0X9B和0X96寄存器,并且需要将0X96 bit 4=1 enable crosspoint。

我们的问题还没有解决,请支持

问题一:在Retimer的输入、输出都有P、N的交换,请问可以配置哪个寄存器来改变对应的channel。是修改FIR的main、pre、post参数?

A: 是的,如果输出driver极性相反,可通过修改这三个参数。-----是不是FIR main(FIR_C0_SGN),pre(FIR_CN1_SGN),post(FIR_CP1_SGN)都需要设置?还是只需要设置其中一个就可以了?其中FIR_CO[0-5],FIR_CN1[0-5],FIR_CP1[0-5]是否保持其默认值就可以了?

问题二:为了走线方便,我们需要在Retimer做内部逻辑交叉,比如输入1B交叉到输出1A、输入1A交叉到输出1B,寄存器该怎么配置?

A: 建议参考datasheet中7.3.4 Cross Point Switch的介绍,需要修改0X9B和0X96寄存器,并且需要将0X96 bit 4=1 enable crosspoint。

0x96(EQ_DATA_MUX_IN[0-1]),0x9b(EQ_CTRL_MUX_IN[0-1]),选择channel时,是rx为准,选择tx channel; 还是以tx为准,选择rx通道? (比如说1a->1b,是选择1a channel(0xfc选择1a通道),配置0x96,9b为1b;还是选择1b通道,配置0x96,0x9b为1a ?)

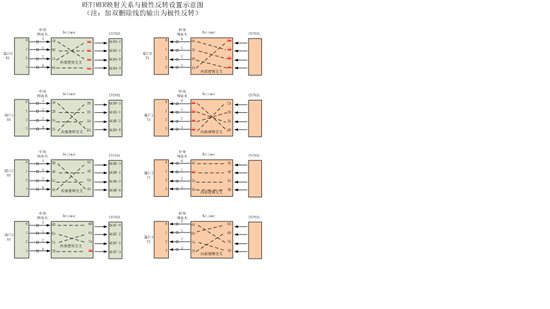

单板上retimer的逻辑关系请看截图:

比如输入1A交叉到输出1B,同时tx(1b)有极性反转。寄存器该怎么配置?能否举例说明?

疑问1:比如0xfc选择通道时,是选择1a,还是1b?

疑问2:fir main的FIR_C0_SGN, pre FIR_CN1_SGN, post FIR_CP1_SGN需要配置成什么值?

对于每个通道我们配置了如下寄存器,及其值,帮忙看下有没有问题?有没有遗漏寄存器没有配置?或者能否提供一下retimer寄存器配置的demo?

急,在线等!

以下是(1B IN ->1A OUT, 同时1A极性反转)

addr, value

--retimer1 select shared reg

0xff, 0x00

--25m clock

0x02, 0x00

--set allowed max locked channel

0x05 0x0f

--retimer1 select channel reg

0xff, 0x01

--retimer1 channel00

0xfc, 0x04

--cdr reset

0xa, 0x54

--adapt mode

0x31, 0x40

--date rate select

0x2f, 0x66

--fir config

0x3d, 0x75

0x3e, 0x03

0x3f, 0x87

--cross point

0x9b, 0x03

0x96, 0x1f

--cdr reset release

0x0a, 0x50

还有cross point switch功能,在8.3章节Initialization setup中是可选配置。但0x96,0x9b寄存器默认是全0,那不是4个rx channel都到tx channel 0去了?

是手册错了,还是怎么回事?能解答一下吗?

急呀!

FAE搞不定,厂家支持回复也这么慢

黄花菜都凉了!

问题还没解决,请提供支持!

关于retimer 的lock:0xa bit[0-1]写1后,查询0x78 cdr 是可以lock的。请教下这样的lock是否正常,我们怀疑这是强制lock,是假lock。

现在功能还没有调好,请给一个retimer可以正常lock的demo(寄存器尽量详细)

对于retimer的5A通道,我们的配置顺序如下,请帮我们检查下,有没有问题,万分感激!

addr, value

//init step

//reset retimer

//select retimer1 shared reg

0xff, 0x00

//25m ref clock

0x02,0x00

//select retimer1 channel reg

0xff, 0x01

//select retimer1 channel 10

0xfd, 0x04

0xfc, 0x00

//cdr reset

0xa, 0x1c

//Adapt Mode Configuration

0x31, 0x60

//enable dfe

0x1e, 0xe1

//date rate select

0x2f, 0xb6

//no fir inverse

//no cross point

//CTLE Bandwidth Select

0x8d, 0x00

//Edge rate control and VGA Configuration

0x8e, 0x02

//enable cdr lock and signal interrupt

0x79, 0x13

--cdr reset release

0xa 0x00

再问个问题,

我们的MCU lane用的是10G(10.3125), retimer data rate(0x2f[7-4]), 设置为0xb6。 retimer寄存器0x34显示有ppm err, 这是为什么?是不是data rate配置有问题?