CDCE52005上电后就能检测到PLL_LOCK为高电平

时间:10-02

整理:3721RD

点击:

上电后就能检测到PLL_LOCK为高电平,用430单片机写寄存器,用示波器可以看到时序是正确的,但是写不进去,也读不出来数据,这是怎么回事?原理图是参考TI 的C6678evm设计的

读写不进去,需要看下 SPI_LE的时序是否正常,它是控制SPI 的使能信号。可看下Figure1&2的读写时序。

片选信号测试时序跟芯片手册一致

片选信号跟哪个时序一致?上电时序呢?注意当power down由低到高变化时,SP_LE还需要为高。

另外,是所有寄存器都无法写入吗?检查下Reg8 的power down和sleep状态。

我的程序是这样编的:上电后将SP_LE拉高,再将POWER DOWN拉低再拉高,然后传数据时片选拉低,传输32位数据后再拉高,时序是符合芯片手册中的要求的。硬件中的49及以后的引脚因为在芯片底部,人工焊不上所以没有焊,这会产生影响么

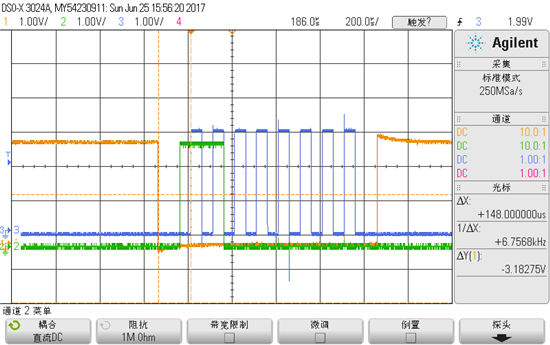

这是用示波器抓到的图,黄色为SP_LE,蓝色为时钟,绿色为MOSI

恩这个时序没问题,CDCE62005是48pin的,没有49pin,QFN封装,带有thermal pad,这个是需要铺铜接地用来提高散热的。

我每发送一个字节数据,430都会接收到一字节来自cdce62005的数据,这个正常么