给dsp28335供电的有源晶振输出只有500mV,直流偏置1.5V

给dsp28335供电的有源晶振输出只有500mV,直流偏置1.5V,但是dsp还能正常工作,有源晶振的封装是7050的30MHz晶振,请问这个晶振有没有问题?

亲;用啥工具测的电压?

示波器,带宽100MHz,足够XP

亲;用啥工具测的电压?

亲;示波器探头是1:1的还是1:10的?探头带宽多少?

有可能是和晶振连接的两个电容值不匹配导致。

亲:

Kailyn Chen

有可能是和晶振连接的两个电容值不匹配导致。

由于有1.5V直流量;0.5V时钟叠加后的幅值不满足DSP逻辑阀值条件;原则上;DSP不应该正常工作。因此;更多可能是探头测量衰减的结果。

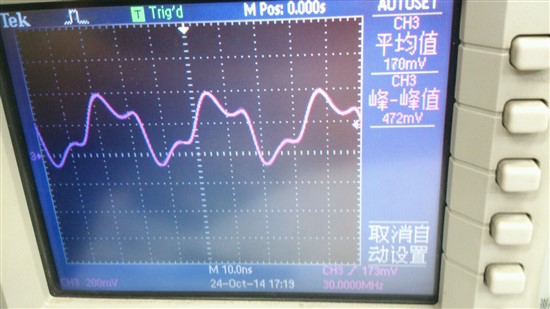

原来是示波器乘1的探头带宽不够,下图是换用乘十的探头测得的结果,输出是这样的吗?为什么还会有负值?XP

亲;示波器探头是1:1的还是1:10的?探头带宽多少?

亲;你的时钟是对的,幅值及周期都没大问题。只是由于阻抗匹配问题;导致显示波形有点畸变而出现了负值,实际板上的波形并不完全是这样,不用太担心。

你的意思是实际的波形可能是标准的方波,只是测量的时候出现了畸变吗?XP

亲;你的时钟是对的,幅值及周期都没大问题。只是由于阻抗匹配问题;导致显示波形有点畸变而出现了负值,实际板上的波形??不完全是这样,不用太担心。

亲;是的,从波形看;实际波是沿不是很陡的梯形波,近似方波。

测量为什么会造成这种畸变呢?测量线的带宽和示波器的带宽不是足够嘛?XP

亲;是的,从波形看;实际波是沿不是很陡的梯形波,近似方波。

亲;正是探头阻抗太高了;造成高频信号反射叠加,引起了波形失真。在探头端口并数百欧姆电阻可以改善这个失真。

亲;不知理解了没有。这个现象与电视机从影是一个道理。

在将时钟信号接入dsp的时候是不是可以串一个100欧姆的电阻来减小这种畸变?还是说应该并联100欧姆呢?XP

亲;正是探头阻抗太高了;造成高频信号反射叠加,引起了波形失真。在探头端口并数百欧姆电阻可以改善这个失真。

只是测量需要;不用管它。

我看到有些有源晶振输入时串了个电阻,也有人并了个电阻,不知道哪一种比较好XP

只是测量需要;不用管它。

亲;你现在的频率还没高到需要匹配的地步。只有66MHz及其以上级别时;才是必须的。

30MHz的波形应该不会这么差,LZ不妨改换一下 示波器探头上的地线夹子 在PCB上的接地点位置。

那66MHz以上是要串电阻匹配还是并电阻呢?XP

亲;你现在的频率还没高到需要匹配的地步。只有66MHz及其以上级别时;才是必须的。

如果就是这么差呢?是什么原因?WEN JAMES

30MHz的波形应该不会这么差,LZ不妨改换一下 示波器探头上的地线夹子 在PCB上的接地点位置。

亲;一般是接收端并电阻。对于数字信号;只要波幅不超极限和杂波小于阀值,可以不用管。

那为什么有些人说是串联电阻呢?哪种效果好呢XP

亲;一般是接收端并电阻。对于数字信号;只要波幅不超极限和杂波小于阀值,可以不用管。

按射频理论;是输出口串电阻;输入口并电阻,用以阻抗匹配。效果由阻抗的一致及稳定性和准确性决定,与串、并无关。

由于实际的标准逻辑口寄生有电阻;所以;对这个应用;即便不做任何处理;失配也不会有大的问题。

好的,谢谢。XP

按射频理论;是输出口串电阻;输入口并电阻,用以阻抗匹配。效果由阻抗的一致及稳定性和准确性决定,与串、并无关。

由于实际的标准逻辑口寄生有电阻;所以;对这个应用;即便不做任何处理;失配也不会有大的问题。

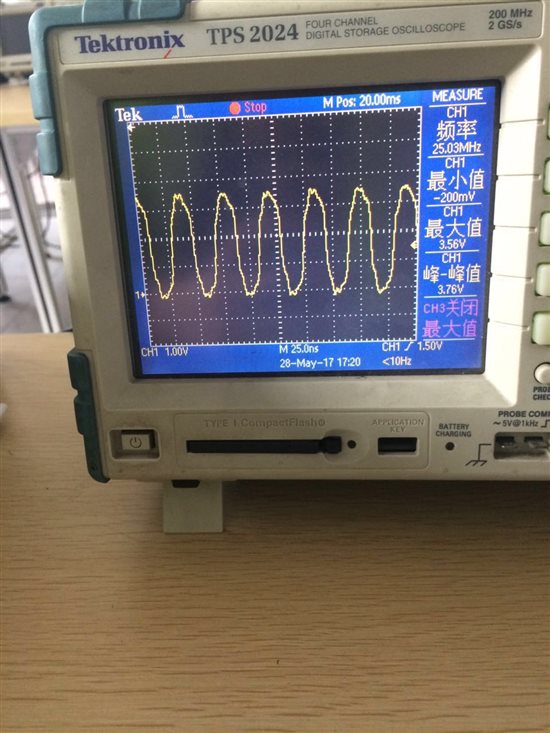

您好,我想问下我的晶振的波形对么?25M的有源晶振,用在dsp上的。理论上说波形不应该是方波或者正弦波么?谢谢

您好,我想问下我的晶振的波形对么?25M的有源晶振,用在dsp上的。理论上说波形不应该是方波或者正弦波么?谢谢