MLVDS(sn65mlvd207)收发器在与FPGA串行通信时(用同一FPGA时钟收发)速度在30Mbps时出现乱码。。陷入了困惑,无法解决。求答案

初步怀疑是时钟同步的问题,可是网上关于时钟同步的解决都是基于自己设计的的模拟电路收发器。有没有其他模块(芯片)可以与MLVDS收发器对接的解决时钟同步的问题或者其他的解决方案,。。。

好像没见到有类似芯片可直接实现时钟同步的。

可以考虑用异步串行方式进行通信,我们就是这样做的

当下也是异步串行方式进行,但是出现了如下问题:FPGA产生数据通过IO口输出,然后通过IO口输入至FPGA接收,8位一帧,设置有帧头和帧尾。发送速度达到25M以上的时候,接收端和发送端IO口的波形不一致。在速度达到40M以上,完全不一致(主要是1位的位宽在接收端变窄,部分出现消失的问题)。不清楚到底是什么原因。。

端接和匹配电阻有吗,多少个从设备会出现问题?

我们这测试65M 10来个模块没问题,再多还没试

一对一到100M很稳定

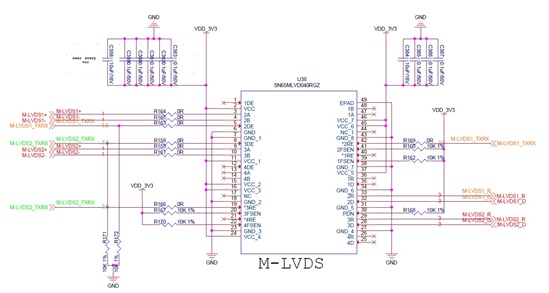

MLVDS芯片采用的是(207),一个接收端,评估板上测试,端接电阻100欧(接收端),接受和发送端的匹配电阻50欧(扣除)。FPGA输出端口电压3.3V。供电电压恒压源(3.3V)。

如果 接受和发送端的匹配电阻50欧不扣除,接收端没有信号。。。。

出现接收和发送的波形不一致。是不是配置的问题?

1.原理图左侧的R1 和R3阻值太小了吧?默认上下拉k级的好一些

2.右侧为什么加了R4 R5 R6 R7这么多端接电阻?你的总线上一共有多少这样设备挂着?

一般mlvds总线驱动器是电流驱动,多个从设备都带这个100欧姆端接电阻是不行的,只能在总线两端加

我图上右边打红X的都是扣除的。左边的R1和R3也扣除了。端接电阻只有一个100欧

你给r8 r9 r10 r11换为10欧电阻试试,是不是信号反射导致畸形了,同时端接电阻R5 和R6改为80欧

另外没听明白你说的端接电阻只有一个100欧,是总线上只有一个设备有100欧姆端接,其他设备都没有吗?

更改后,还是不行。能否参考一下你们的设计?2016779848@qq.com

您好,问下您电路图中从A,B端出来的串联电阻是多大阻值的啊?我们设计的时候没有这个电阻,但是拷机测试的时候会出现少量的误码情况?会不会是这里没考虑到所引起的?同时测得信号质量较差,总线上总共有16个点,信号的过冲和回沟较严重,想问下你们设计的时候有没有碰到这个问题?后面怎么解决的呢?

那个端接电阻稍微有点用,不起决定性作用 你看看你的pcb,每个节点分线岔长度是不是太长了 ti官网上有一篇国半的测试报告,对信号质量说的很清楚 节点越多信号质量越差,另外type1容限比2好很多,你可以试试

对这个分叉长度有什么要求么?那篇测试报告能不能提供个链接啊?我们的设计方案为MLVDS总线信号在PCB上走线至连接器,PCB上的走线长度为1260mil左右(3.2cm),差分线偏差在2mil左右,连接器通过接插件至背板,连接器的针长为1.3cm,也即分支节点的长度总共为4.5cm,会不会太长了?MLVDS的节点能最多支持32个点吧,我们只有16个点,没有超过这个理论值。同时我们是一个背板一个机笼,现在是两个机笼进行级联通信,每个机笼有8个点,之前本来是进行一个机笼的总线通信的,所以一个背板上是能够形成回路的,但是两个机笼级联,就将背板上的一段的匹配电阻去掉了,现在相当于有残线在两个背板上,残线长度大致为3.5cm,不知道这个残线会不会对信号产生较大影响呢?

31960248 你加我qq说吧

已经申请发送申请了,麻烦您同意下,我QQ号286220486