急需TUSB1310A的技术支持

您好:

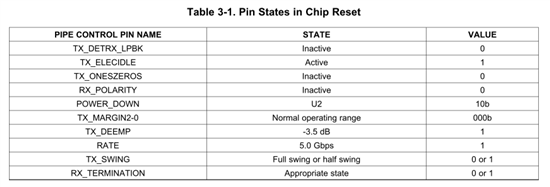

我们公司现在正在用TUSB1310A,这款PHY芯片做整个USB3.0的phy部分,现在我们的控制器与该phy通过pipe接口对接之后,在进行usb3.0的FPGA测试的时候,发现该phy没有正常工作,TI的网站上只有几个文档资料,包括芯片手册等,并没有其它相关phy的配置信息(phy的配置驱动程序、软件开发包等资料),看了PHY的手册,也有一些寄存器配置,但是我们不知道如何配置。另外,现在我们的phy的复位RESTEN已经释放了,但是我们读到的Pin States跟下面表格里面的一样的值,好像还是处于复位的值。

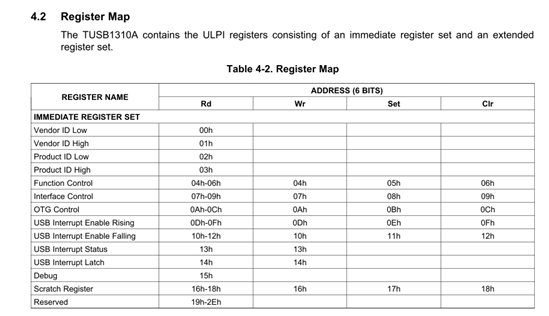

phy手册里面寄存器该如何通过软件配置呢,USB3.0的模式该配置哪些寄存器?

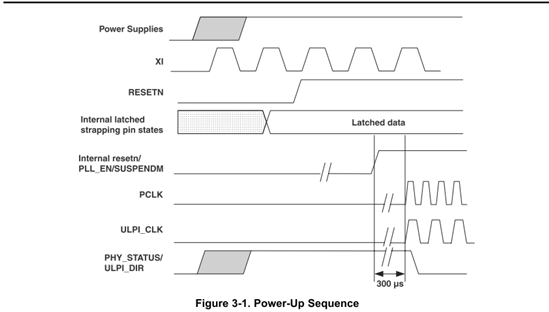

还有一个问题就是有关PCLK的时钟稳定延迟时间,和上电的先后顺序,这个具体该如何去通过软件配置和控制呢?

我的邮箱是838159288@qq.com。也可以通过邮件与您交流。

期待着您的回复,非常感谢!

是否已经避免了errata中列的问题,另外在Reset前,测量各个供电电压和振荡器是否已经工作?

非常感谢您能回复我的问题!

errata中所列的那几项,跟其中一项的问题基本一致

RX_ELECIDLE low (it should be high ) when not receiving a valid LFPS.

但是errata上面并没有解答该问题。

各个供电电压已经确认过了,没有出现异常,并且PHY芯片内部的PLL也可以正常工作,PLL能够正常锁定。

其实关于TUSB1310A,我们这边也是第一次用,手头上能够参考的东西仅仅是PHY的手册文档和errata,关于详细的TUSB1310A配置信息都没有。

之前也用过其它厂家的PHY,都是给提供一套PHY芯片正常工作的初始化配置的软硬件流程。

现在急需你们的技术支持,之前还有这个PHY的调试经验吗?烦请你们再给我们提供一些可参考的信息,谢谢!

不好意思这几天没上来看。这个PHY本身初始化配置是相对OK的,应该说没什么可配置的因为要怎么设置是要看你们USB是什么角色/link layer的状态机是什么位置,PHY本身没什么东西好配置其实,设置一下中断,然后就是根据link layer的状态来做interface control。那个errata没问题的,可以不用这个pin来判断连接状态。你可以参考下面这个项目的代码,以及首先确认你的芯片焊接是没问题的。

https://github.com/mossmann/daisho/tree/1d2f5e1cb16a9a724f957cc6c99e63b601e5cac0

还有关于rx elecidle不正确的替代处理,Wes Ray的回答:

http://e2e.ti.com/support/interface/digital_interface/f/130/p/108483/400941

非常感谢您的回复!

我们现在在FPGA验证USB3.0的时候确实遇到了很大的困难。

刚才看了你发的那个帖子的链接,其实我们现在遇到的问题,跟帖子上面的问题是差不多的。

The rxelecilde is toggled normally after I reset my U3 host.

Now I go on LTSSM to receiver detection by power_down[1:0]=2'h2, tx_detrx_lpbk=1 and tx_elecidle=1.

Then I wait phy_status asserted and check rx_status[2:0], but the phy_status is never asserted.

Even I switch power_down[1:0]=2'h0, the phy_status is also not asserted.

The phy_status only asserted during reset assertion.

都是在RESETN和PHY_RESETN 释放后,Pipe3_powerdown一直处在2(P2)的状态,phy_status的状态一直为0,只有在复位的时候才为1 ,正常情况下PHY_STATUS在 复位释放后应该出现高电平的脉冲。

最关键的是RESETN和PHY_RESETN 释放后,RX_STATUS一直为0,导致现在LTSSM状态机一直停留在5状态,没有继续往下跳。

能否留一个您的邮箱呢,这样方便请教您,感谢您对我们工作的支持!

请问有芯片的测试程序吗?