SDIO接口3.3V至1.8V的电平转换使用TXS0108E的问题

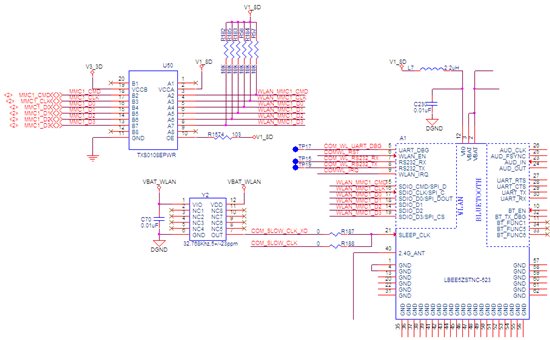

参考AM335x starter kit开发板,将SDIO1接到LBEE5ZSTNC-523m(WL1271L)模块。

在设计中将AM335x的MMC1 IO电平置为3.3V,因此需要用到电平转换芯片。

请问如图所示,将SDIO的数据线、命令线、时钟线用一个TXS0108E作电平转换,是否可以?另外,外接的上拉电阻是否正确?

谢谢。

Hi Zhaohui,

电路没有什么问题,推荐在VCCA和VCCB管脚上加上去耦电容。

Hi, Nick,

感谢答复。

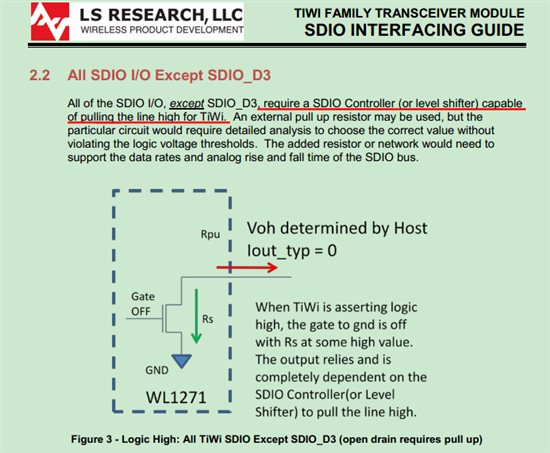

SD时钟信号的最大频率为25MHz,直接这样进行电平会不会有问题?根据LS Research的一篇文档,WL1271的SDIO接口除了SDIO_D3外,均为开漏。如果工作在开漏模式下,则TXS0108E的速率应该达不到25MHz。

Hi Zhaohui,

你用下滑红线标注的部分正说明SDIO的接口需要主设备提供上拉,开漏结构的逻辑接口需要上拉才能正常工作,如I2C。

所以上拉后的速率没有问题。

Hi, Nick,

感谢回复。

TXS0108E datasheet中提到:

Max Data Rates

– 60 Mbps(Push Pull)

– 2 Mbps(Open Drain)

当工作在开漏时,只有2Mbps,不够SDIO速率吧。

Hi Zhaohui,

你在电路上做了上拉处理,所以速率没有问题。

我看了一下SDIO的标准, TXS0108E的问题在于CMD信号。SDIO在初始化时为了非常准确和稳定的同步使用的是OD模式,然后在数据传输时切换到上拉模式已达到更高的速率。

鉴于SDIO特殊的工作模式,你可以看一下TXS0206,这个应该更适合你的应用。

Hi, Nick,

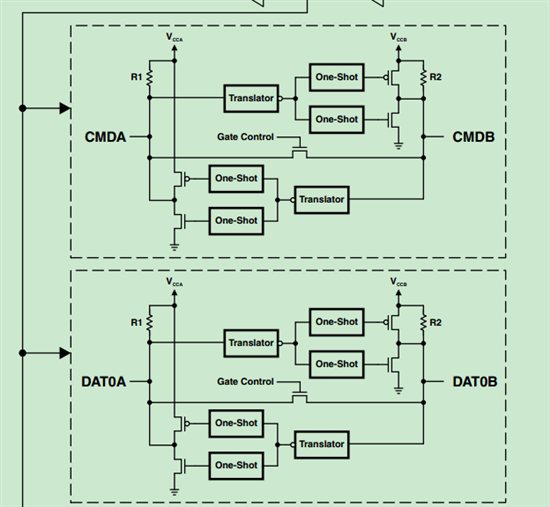

如图所示,TXS0206内部的CMD结构与数据线似乎没有什么区别,且都与TXS0108E类似。

为了方便焊接与维修,因此我比较倾向于不使用BGA封装的,谢谢。

您好,,我的应用是:A侧作为SPI的SCK输入,A侧1.8V电压,B侧3.3V。SCK引脚是否支持下拉电阻1kΩ。在Datasheet第21页有这样的描述:

• An external pull-down resistor decreases the output VOH and VOL. Use Equation 1 to calculate the VOH as a

result of an external pull-down resistor.

VOH = VCCx × RPD / (RPD + 4 kΩ)

若下拉1K电阻,输入高电平就是1.8/5=0.36V,那么A侧输入0.36V就是高电平了,低于0.36V就是低电平,可以这么理解吗?

作为SPI通信,若想SCK默认电平为低电压,您的推荐硬件电路该怎么设计呢?

期待您的回答,,多谢!

hi,请教一下,我在使用TXS0108E是遇到输出端波形上升斜率小,就是上升时间较长,矩形方波波不够理想,这是什么原因造成的?

ps:a端和b端均没有接上拉电阻。

你好,nick,

请教一下TXS0206和TXS0206A有什么区别?