CDCE62005 输出时钟问题

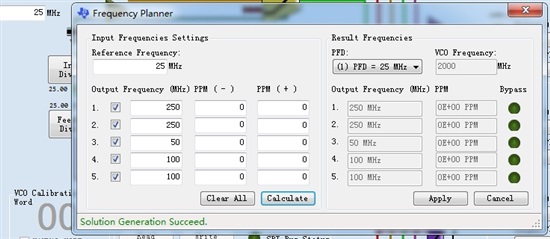

CDCE62005 只有AUX 25M晶体输入,输出250M,250M,50M,100M,100M

没有主/从参考时钟,在CDCE62005 EVM software中 环路滤波器应该怎样计算。

现在250M 实际输出93M ,而且很不稳,请问主/从参考是不是必须用一个呢?

另外,读寄存器PLLLOCK时,是不是先向寄存器8发一个命令,再读数据呢?

可以采用AUX晶振输入,主从参考可不使用,CDCE62005三种输入模式,AUX,主从参考,smart MUX三种。250Mhz输出有问题,其他通道输出是否也有问题?

采用EVM software配置的寄存器?

上面的参考频率输入的是 AUX 晶体的频率吗?

各路输出信号,频率高的幅值非常低,是不是示波器测量不准,还是阻抗不匹配?我采用的是交流耦合方式,电容为0.1uF,接收端c6655 各路时钟,没有并100欧电阻。

另外,CDCE62005输出的信号是正弦波还是方波?

这里的参考时钟输入应该是主从参考,不是晶振输入。

你配置的各路输出是什么电平标准,LVDS还是LVCMOS?

虽然VCO输出的正弦波,输出应该是方波。

那现在没用着主从参考频率,怎么计算环路滤波器的参数,各路输出

都是LVDS.各路信号频率输出越高,电压幅值应该不变,还是变小?

试了好久这个GUI,frequency planner里的参考应该指的主从参考,并且没有办法设置AUX input,这个我需要再确认下。

环路滤波器倒是 里面有个Tool,点击打开,通过设置环路带宽,得到相应的RC值。

至于幅值和频率的关系,在CDCE62005 datasheet Page12中有关于LVPECL,LVDS,LVCMOS 几种output swing跟频率的曲线。可以直接参考幅值随频率的变化曲线。

Cdce62005 输出频率和设定有偏差,例如100MHZ,实际108MHZ,如何处理一下?