SN65LV1023/1224接收数据乱码

时间:10-02

整理:3721RD

点击:

通过FPGA控制SN65LV1023/1224进行并串转换,接收数据出现错位。输入时钟为54MHz。

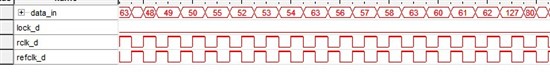

通过逻辑分析仪获取到的数据如图:

请问这种情况都可能由哪些情况导致或引起?该如何解决?

同步过了么

同步过了,每次发送之前都进行初始化、同步,然后才发送。每次发送1000个数据。之前发送和接收放在一块板子上是没有问题的,现在分开,就出现这样的问题了。

发送和接收端距离有多远?

50cm长左右的屏蔽线

如果同步过了,要看下参考时钟的抖动是否太大?因为一般情况个,整个串并转换的抖动是有要求的,只有发送端的抖动尽量减小,接收端的余量增大,才会减少误码率。

我试试,谢谢。

再次谢谢,问题已经解决,是恢复时钟的问题,对恢复时钟进行隔离后解决了该问题。还有一个串行器/解串器选项方面的问题想请教:TI有没有同步时间短、并行位数在8位以上的芯片,如果有评估板的话最好。此外,有一个原理上的问题:对于点对点之间的串行器/解串器,完成同步后,如果中间通过高速开关切断连接,恢复之后是否必须再次进行同步?有没有不需要再次进行同步的芯片?谢谢。

恢复时钟进行“隔离”后解决了该问题 ----------“ 隔离”是啥意思呢?

用地线进行包裹。

我想请问一下:同步时钟是异步时钟吗?时钟信号是不是也和数据信号一起传输?目前出现的问题和上边提到的一模一样