多个同类型的AD和DA芯片是否可以使用同一条时钟线?

我现在使用的2片同类型DA、5片同类型的AD芯片都没有内部时钟,需要外接时钟。

DA芯片需要的时钟频率是6M,DA的时钟频率要求是40M。

我用FPGA控制它们。FPGA内部有两个可编程的PLL。

1、不知道可不可以将一个PLL的输出连接到两片DA上,另一个PLL的输出连接到5片AD上呢?

2、如果使用时钟芯片的话,有什么好的芯片推荐吗?

如果使用时钟芯片,可不可以让1路输出连接到2个DA,另一路输出连接到5个AD呢?还是得用7路时钟输出分别驱动每一片芯片?

如果使用时钟芯片,FPGA是不是也就不用使用外部晶振了,直接用时钟芯片产生的时钟就可以了呢?

3、关于这个项目时钟方面的内容,有什么难度吗?有什么更好的建议吗?

谢谢

可以但是不建议,因为驱动能力和jitter都会有问题

不是高手不要这么做

用clock buffer进行分配吧

CDCLVC1102和1106就是干这个用的

如果用时钟芯片的话,可以考虑CDCE62005.

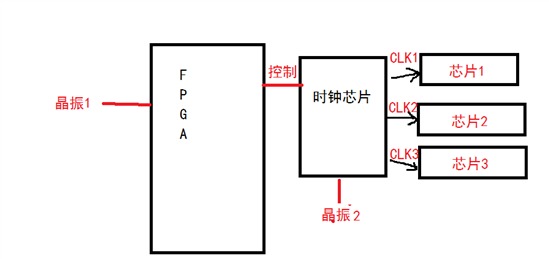

像图上这样应该就可以吧~

另外,FPGA是3.3V的电平。CLK是5V电平。有这种可以转换电平的时钟芯片吧

是的

是这种拓扑结构

什么ADC和DAC需要5V的clk

很抱歉,是其他公司的一款DA芯片。在TI公司并不能找到类似的芯片,其实我更愿意用3.3V电平的芯片,可实在找不到

芯片要求:

最低16位,速度在5M以上。用起来方便。

速度太高的芯片,如500M,实际用的时候加入CLK用20M的,这样可以吗?如果这样,还有什么其他需要注意的问题吗

谁家的无所谓。关键是要看一下5V供电的。它的电平的规格。有可能和3.3V的是兼容的

可以在500Mh的芯片上跑20M的速率。但是要注意有些芯片有高速和低速的模式。

电平不兼容,数字信号高电平最低为3.5V。好的,谢谢你啦~

不过我还是觉得TI的东西靠谱。TI有没有多路电平转换器可以用啊