求 TI 大神来讲解 DS90C365 芯片

方案 :LPC单片机 控制DS90C365,尝试驱动 14寸液晶屏

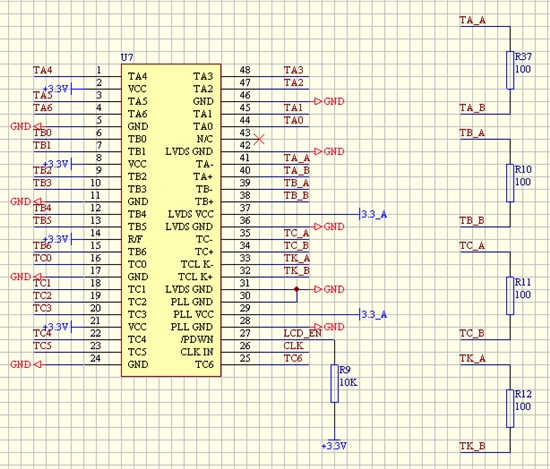

下面为 原理图, 板子上焊接的为 DS90C365:

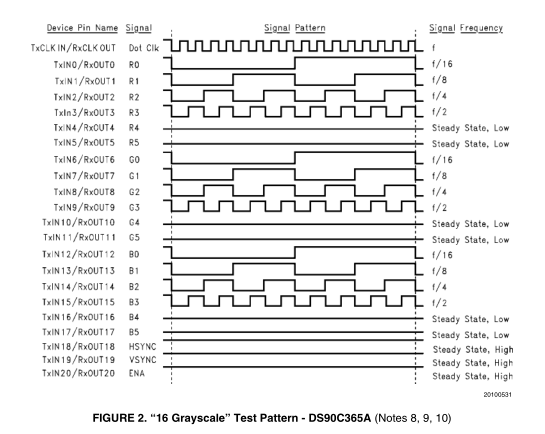

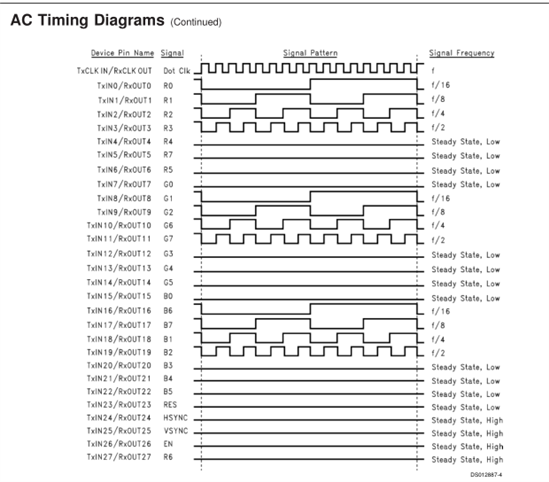

根据DS90C365 手册时序图

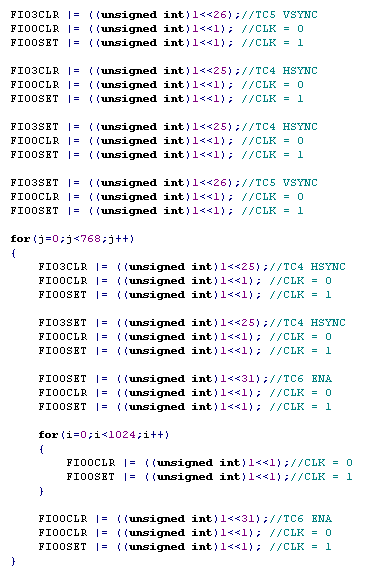

我把 所有的输入脚都写成 高电平,然后 时钟 循环一直送高低电平,HS,VS,ENA 全部为高,

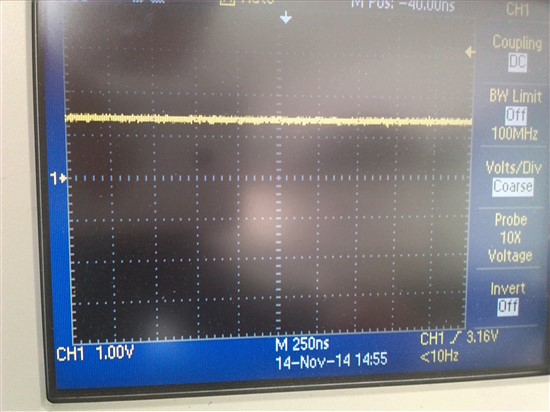

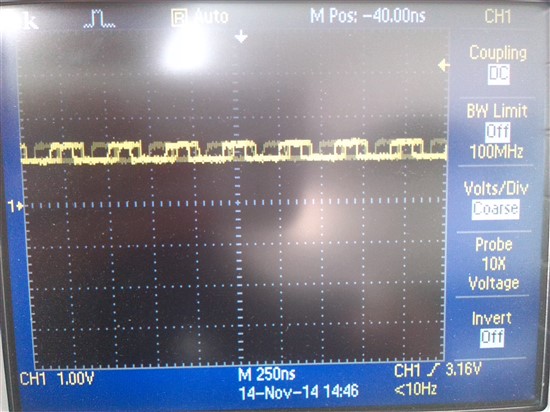

TA- 波形

TA+ 波形

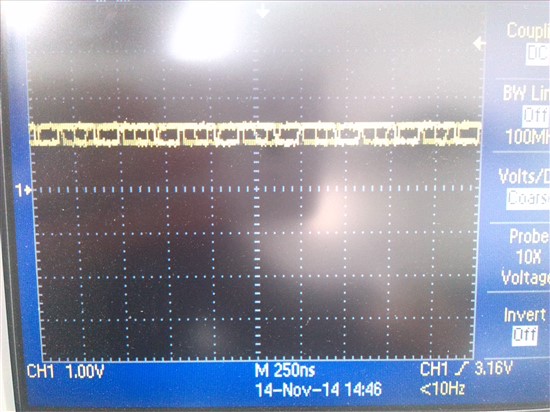

TB- 波形

TB+ 波形

TC- 波形

TC+ 波形

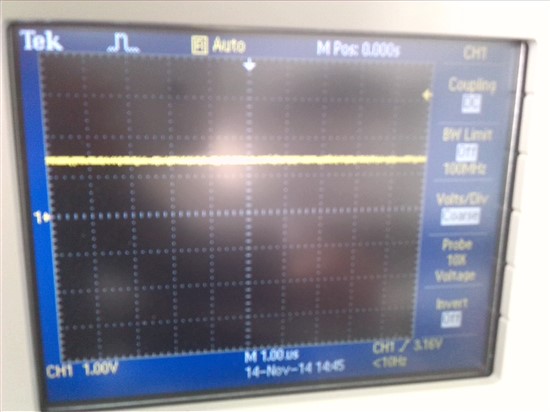

TCLK- 波形

TCLK+ 波形

为什么 LVDS 输出,有的连波形都没有呢 ? 请问下 我应该怎么办呢

LVDS差分输出有没有在靠近显示屏端接100ohm终端匹配电阻?如果显示屏内部已经集成100ohm匹配电阻了,就不需要接了。

1、电阻 我接了,100欧姆的,

2、这几个波形,我就是测量电阻脚测出来的,我怕屏会影响到时序,我屏线没有接上

3、我看时钟TCLK 怎么没有波形呢 ? 是不是我哪里设置的不对,或者接的不对啊

我现在还不是很清楚 TxIN0-TxIN17数据端口数据是怎么送的,我是随意的设置了高电平或者低电平, HS VS ENA 都为高电平,

然后我就设置 时钟 高低电平 循环切换,上述 波形就是这样测试出来的

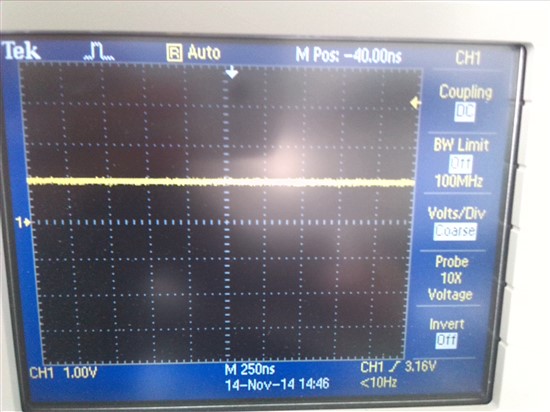

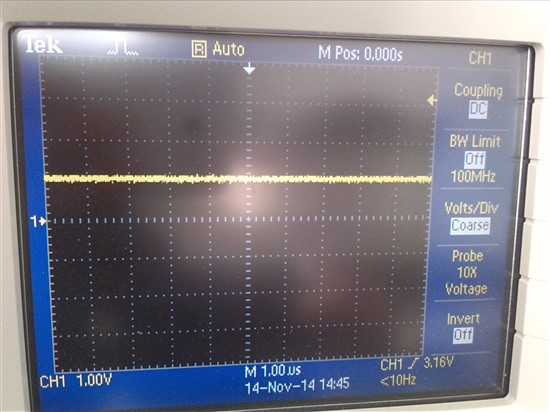

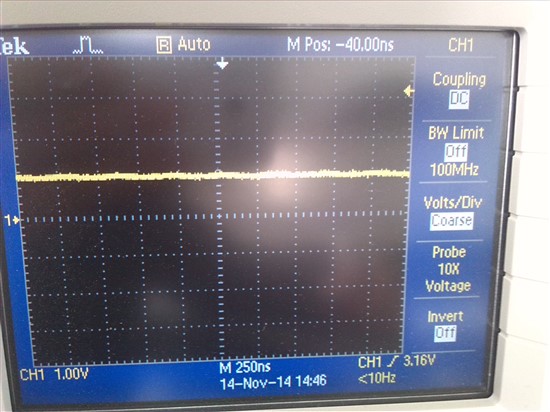

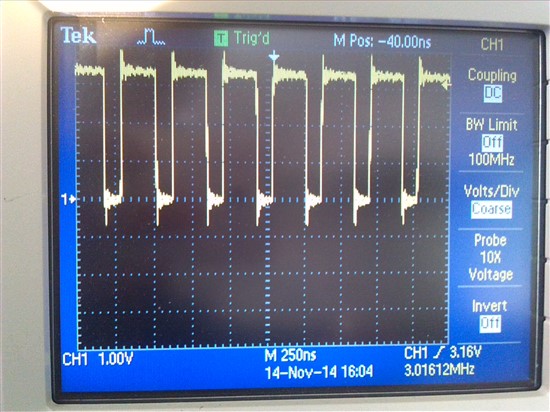

TCLK IN 输入时钟 波形

这个是 输入时钟, 这个频率 有影响 吗 ?

哪位 帮忙看下啊, DS90C365 正常工作时, TA TB TC TCLK 波形是什么样子啊 ?

顶一顶。请大家帮忙看看啊

这个频率没有问题,TCLK的周期范围为11.76ns~50ns,频率为1/T,在这个范围内即可。

TxIN0-TxIN17还有同步信号HSYNC,VSYNC都是主控发的,并且HSYNC,VSYNC不应一直为高,应该是个固定频率的方波才对

感谢 您的回复。

1、TCLK IN 时钟是对了,但是 输出的时钟 怎么没有波形呢 ?

2、我看时序图 上 HS VS ENA 都是高啊,如下图。 如果这样不对,我该怎么设置呢 ?

这个时序我认为有问题,我记得VESA标准中的同步信号都是方波,并且之前做过的VGA的时序中HSYNC,VSYNC也是方波,而不是一直为高。这个需要核实下。

DS90C365是 成熟的芯片啊,应该有很多成功的案例吧。

我是刚开始做这个,项目已经好长时间了,一直没有进展,着急

还得麻烦您看一下

查资料 HS VS 是用来消隐的。

HS VS是不是还有切换行、场的作用呢 ? 加入现在在第一行,送行点数*3个时钟之后,再送 HS, 行信号是不是就移动下一行 最开始的位置,以此类推 ,送完整屏 ,再送一个 VS 场同步, 是不是应该重新送下一屏的数据

求 TI 大神来帮忙 看看 DS90C365芯片,急。

究竟 怎么样 来理解这个时序呢

您好,请问DS90C365是LVDS发送芯片,也是LVDS接收芯片吗?

只是一款发送器件哈,不是集成发送和接收的serdes,如果需要和DS90C365搭配的接收芯片,可看下DS90CF366.