关于CECE913的电压控制脚的问题, 请朋友们帮忙解答?

时间:10-02

整理:3721RD

点击:

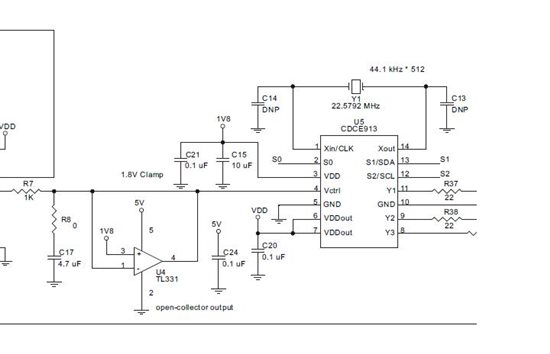

我在产品中使用用CDCE913 (3.3V) 做PLL, 因为Vctrl 的范围是0~1.8V的, 所以参考设计的此脚加了一个比较器做箝位(到1.8V),

我的问题是?

1.我是否可以在鉴相器输出端(低通滤波前)用一个3.3V->1.8V 的电平转换器, 而不用这个箝位比较器。

2.如果可以, 在性能方面有什么不同?

3. 说明一下,这个箝位比较器是怎么工作的?

请帮助解答,谢谢各位!

图片来自 TI Scaa088

你好

我看不到完整的原理图,但是这个比较器应该只是做一个保护的钳位:一旦输入的信号超过1.8V,就会把Vctrl拉低,保护VCXO,而不是一直都是个1.8V的电平

你能否说明下TL331之前的电路是怎样的

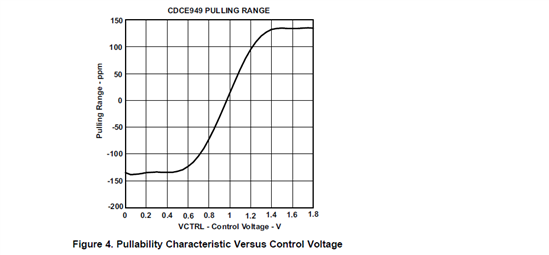

如果直接采用3.3V到1.8V电平转换,那么Vctrl的输入固定为1.8V,而crystal的pulling range是根据crystal的类型,PCB的寄生电容来决定的,是随着Vctrl的不同而不同。你可以看下CDCE9xx系列的fpr对着Vctrl的变化曲线: