CDCE62005读eeprom寄存器时第一个寄存器总是0?

我用TI的62005EVM的SPI口给62005烧写寄存器,烧写到eeprom中,有时上电5路输出都正常,有时上电第一路没有输出,其他4路工作正常,后来发现输出不正常是第一路ram中的寄存器的值全是0,也就是从eeprom中读寄存器值到ram时,第一路读错了,其他4路都正确,请TI员工和技术高手帮忙分析一下,着急啊

请各位帮帮忙啊,着急

Register 0无论写入什么,读出来都是0?

输入和输出频率多少?将其他四路disable,只enable第一路看是否有输出。

你好:

有关你的问题是否可以理解为EEPROM默认配置载入有问题?如果是这样首先确认你目前

1,总共有几块板是否每块板都有这样的问题?

2.出现问题概率有多大?上电多少次有多少次会发生?

3.请注意每次上电power down pin状态,参考手册p37

您好,

1、我有20块板子,每块板子都有

2、常温下十次就有1次

3、我的powerdown pin是悬空的

板卡上电后62005直接工作,powerdown和sync都是悬空的

我是用aux-in输入25M

第一路:输出两路LVCOMS 125M;

第二路:输出两路LVCOMS 125M;

第三路:输出两路LVDS 50M;

第四路:输出两路LVDS 50M;

第五路:输出一路LVCOMS 100M;;

我是用aux-in输入25M

第一路:输出两路LVCOMS 125M;

第二路:输出两路LVCOMS 125M;

第三路:输出两路LVDS 50M;

第四路:输出两路LVDS 50M;

第五路:输出一路LVCOMS 100M;;

请注意这句话:

The SPI_LE status also impacts whether the device loads the EEPROM into

the device registers at power up. SPI_LE has to be logic "1 " before the Power_Down pin

toggles low-to-high in order for the EEPROM to load properly.

SPI_LE has to be HIGH in order for the rising edge of Power_Down signal to load the

EEPROM.

谢谢,我这两个信号SPI_LE和Power_Down都是悬空的,不好设置更改了,有什么办法可以解决么?

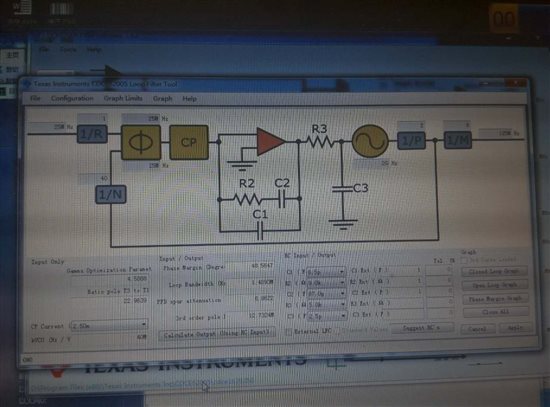

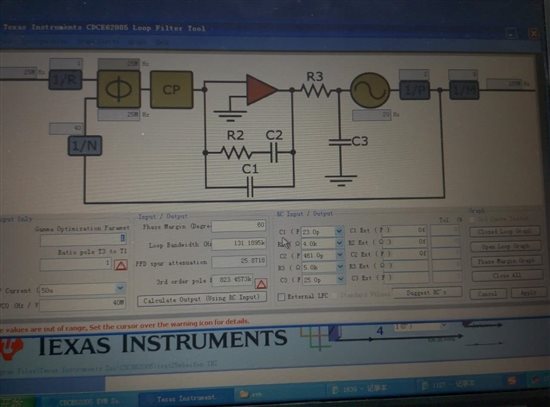

另外在loop filter中有好多叹号,这个是不是一定要去掉叹号,我调整去掉叹号后,输出频率都不正常了

你好:

请按照我们手册相关推荐要求进行上电配置,以保证芯片及系统的稳定工作。你现在可以先飞线测试下,验证看是否根源。

环路中哪儿是报错吗,请具体上图看下。如果你环路设置产出范围,输出就可能不对了。

SPI_LE内部已经上拉,默认逻辑高,所以按理这个引脚悬空应该没问题。

PD的话,按照Robin说的,上电时应有个由低到高的变化过程。 但是其他通道寄存器都能写进去,唯独第一个通道EEPROM没写进去,也很奇怪。

按理说器件电上到2.35V就开始导入默认配置,大概100nS. 但是这种偶发问题就可能和上电过程中的某些管教状态和干扰有些关系。因此可以做的建议;

1.按照我前面的意思:上电后power down一下,这样就确保默认配置应该能导进去了。

2.把上电过程缓一些,例如电源上加一个大一些的电容:看下这个上电时间是否有可能过快或过慢影响到power on reset的执行,问题是否会受到影响;

如果器件完好的,第一个应该是可以确保,第二个需要验证下,谢谢

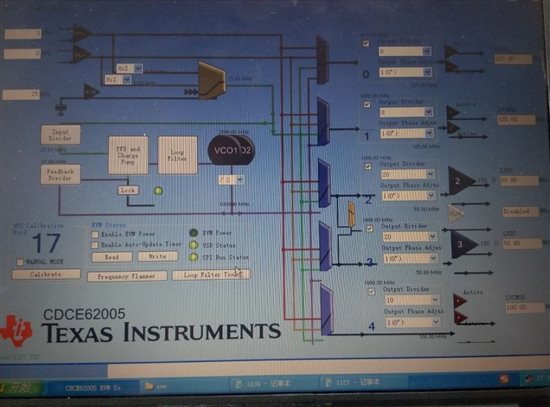

这个图是GUI配置的图片,从aux in 输入一个25M LVCOMS的时钟

在loop filter中有叹号的反而容易lock,调节了一个没有叹号的反而不容易lock了

谢谢您的支持,我做了第二个测试没有改善,第一个测试明天测试,我上传了我的loop filter,请帮忙看看有没有问题,谢谢,我把叹号调没有了反而不容易lock了,读寄存器都不对

双击图片看大图比较清晰,谢谢

将其他四路关闭了测试不能lock了

并不是说把警告消了,你的环路就是适合的。把系统调稳定了再去优化环路,列如手册上推荐的那个400k的环路。

- output buffer的使能应该与pll没有关系,你看下是不是哪儿搞错了

帮忙看一下我现在没有叹号的loop filter 有问题么?哪些参数需要调整

对环路稳定性应该有影响,但是与你目前的寄存器加载问题没有关系。

方法1是否验证?结论如何,问题是否解决,请反馈,谢谢