SN74LVTH16245与SN74HCT244接口问题

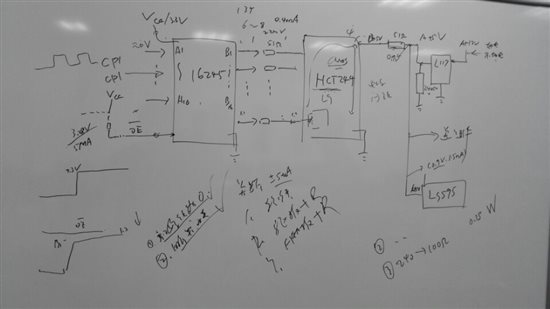

在设计中我们用FPGA驱动探测器。SN74LVTH16245用在FPGA板上,SN74HCT244用在探测器板上,分别作为信号缓冲器,两者之间信号用51Ω电阻隔开。如下图示。

FPGA板先上电,探测器板后上电。FPGA采用Xilinx的VirtexII Pro,采用Master Serial配置方式,上电配置时间约3秒,FPGA板上的SN74LVTH16245的\OE端未连接一个上拉电阻至VCC,由FPGA输出的信号控制,因此在FPGA配置的3秒时间内未能有效将SN74LVTH16245置于3态输出。此时,探测器板未上电,板上的SN74HCT244接收到SN74LVTH16245的输出信号。请问会有什么影响和后果?谢谢!

亲,一般不会有大问题,但有风险。建议将上拉电阻加上。

FPGA板的SN74LVTH245是发送级,探测器板的SN74HCT244是接收级。

那么作为发送级的SN74LVTH245,其输出处于三态 并无益处。

建议 将16位数据线的每一位 都加 上(下)拉电阻,以确保 上电期间 数据线的确定性。

应该没什么影响,一般TI的逻辑产品都有Ioff特性,就是说当power down时候,即使给输入一个高电平,Ioff特性将IO口保持在高阻抗状态。

另外,SN74LVTH16245内部集成Bus-hold电路,不用的输入端可直接悬空也能保持在一个固定的逻辑状态,不需要上拉电阻。

请问,您说的上拉电阻是换16245的\OE端吗?会有什么样的风险?

在FPGA上电配置过程的3秒中,HCT244未上电,由于16245的\OE端未上拉其输出未能有效进入三态,HCT244电源端会有1.6V的电压存在。FPGA上电配置过程结束后,16245的\OE端由FPGA管脚输出高电平驱动,按道理16245的输出应为高阻,但HCT244的电源端有约0.7V左右的电压。我想问的是Ti公司的HCT244可以做为冷负载吗?若HCT244未上电,有信号输入,会有什么后果?16245的\OE端只要加入高电平是否就能有效隔离开两边总线?谢谢!

我说的上拉电阻是针对data线来说的,一般的如果不用的通道,不建议直接悬空,建议上拉或下拉到GND,使其保持在一个有效的逻辑电平防止悬空,但是带有总线保持BUS-hold特性的产品来说,可直接悬空。

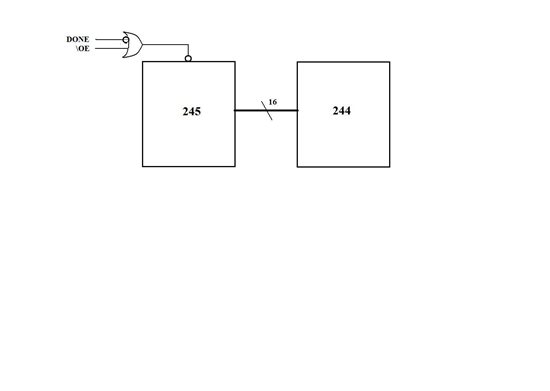

LZ若是希望在FPGA的配置期间总线处于三态,不妨将FPGA加载成功信号DONE加入到\OE的控制中

详见附图

TI的很多逻辑产品中的datasheet一般都具有Ioff的特性,Ioff是这么定义的:Jianwei Li

在FPGA上电配置过程的3秒中,HCT244未上电,由于16245的\OE端未上拉其输出未能有效进入三态,HCT244电源端会有1.6V的电压存在。FPGA上电配置过程结束后,16245的\OE端由FPGA管脚输出高电平驱动,按道理16245的输出应为高阻,但HCT244的电源端有约0.7V左右的电压。我想问的是Ti公司的HCT244可以做为冷负载吗?若HCT244未上电,有信号输入,会有什么后果?16245的\OE端只要加入高电平是否就能有效隔离开两边总线?谢谢!

Ioff - The maximum leakage current into an input or output terminal of the device, with the specified voltage applied to the terminal and VCC = 0 V.The Ioff protection circuitry ensures that no excessive current is drawn from or to an input, output, or combined I/O that is biased to a specified voltage while the device is powered down

因此具有Ioff特性的器件,如果Vcc=0,但是给了输入信号,最大电流不超过Ioff给出的值,那么对器件是没有影响的。HCT244我看了下datasheet未介绍这个特性,或者就你目前的应用,可以考虑像SN74ABT16244A这种具有Ioff特性的buffer更适合一些。

LVTH16245的\OE端为高电平时,若16245的输入端仍有信号变化,其输出端也应为高阻状态。但此时的高阻状态接后端电路(经51欧姆电阻连接至未上电的HCT244输入端)会有约0.4mA的电流流出。这种现象如何解释?谢谢!

FPGA的DONE管脚未引出,其在配置完成前输出一直为低吗?16245的\OE端为高时才能将其设置在高阻态输出。可将16245的\OE端经上拉电阻连接至其VCC端。谢谢!

OE通过上拉电阻到Vcc,datasheet中也有解释,就是为了 SN74LVTH16245在上电或掉电瞬间,输出为高阻抗状态,换句话说,Vcc从0V上升到1.5V时候,输出为高阻抗,当大于1.5V时,内部MOS管导通,OE连接到GND, SN74LVTH16245进入正常工作状态,如果直接将OE拉低,那么MOS管直接导通,一上电就能正常工作,增大了功耗。 当为高阻抗状态时,输出电流不大于100uA。

您好,我目前也出现类似问题,使用的是SN74LVTH16245A,FPGA 2.5V BANK(载卡上)先上电,通过FMC后经过SN74LVTH16245A,给子卡上的ADC供电了,(SN74LVTH16245A上的信号为FPGA给ADC的SPI配置信号),多次上下电之后(没有程序),SN74LVTH16245A前后状态不一,更换新的SN74LVTH16245A后,其前后状态一致,之后调整载卡上FPGA 2.5V后上电,一切正常。

请问SN74LVTH16245A的损坏是不是因为在其上电前,有信号灌流到VCC?手册中提到IOFF有保护作用,但是怎么没有保护成功呢?

另外,DATASHEET中关于内部结构没有VCC的参与,希望有VCC和门电路等的连接关系。

你的意思是SN74LVTH16245A未上电,但有灌电流输入?Ioff的最大电流不能超过100uA啊。