利用fpga配置lmx2541芯片,时序问题

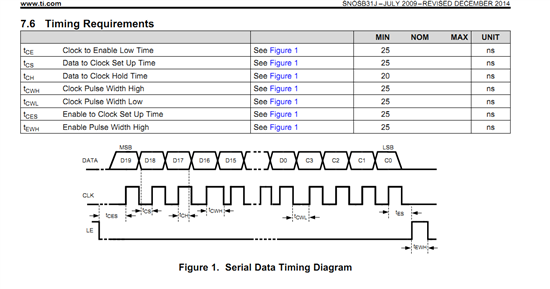

现在第一次搞fpga配置lmx2541芯片,根据芯片手册上的配置时序,按自己的理解是在le电平拉低的时候按顺序写入寄存器值,然后le拉高,然后le再拉低,再写入寄存器值,但是没有输出,请问下有没有配置过这芯片的人,我用的是12.5mhz的时钟给clk端口,rfen和ce直接给1,。想问下这个时序对不对,还有配置clk频率要求。还需要配置那些?本身对pll也不太了解,直接扔过来的任务。。。

还有,请问下ld信号在配置的时候需要判断吗?

下个TICS PRO软件,它可以根据你的需求把要配置的寄存器和对应的值导出来,然后你通过FPGA往里面写。

谢谢你的回答,我的问题不是寄存器值问题,我利用codeloader4软件把寄存器值导出来了,按照手册的时序写进去了,但是rfout输出端口一直是拉高状态,想请问如何调试,是时序问题吗?我需要如何调试,如查看ld引脚是否拉低?fpga写进时序应该就只有le和data引脚时序要求吧?

Q: 根据芯片手册上的配置时序,按自己的理解是在le电平拉低的时候按顺序写入寄存器值,然后le拉高,然后le再拉低,再写入寄存器值,但是没有输出

A: 按照Figure1的时序,LE使能低有效,如果拉高再拉低,所有的寄存器都复位了吧。

datasheet中介绍需要Register7先配置,是因为这个寄存器能复位其他所有的编程信息,而这个复位的动作就是LE从低到高,再从高到低变化的过程。

一般是写powerdown寄存器,看电流是不是变化来验证总线是不是写进去了

调整时序后,fpga电平用的是lvcmos25,每次上电抓取的ld状态都不一样,但是最后都是高电平,这个应该是成功写进寄存器了,但是没有输出

调整了时序,ld端口在写最后两个寄存器时出现变化,最后拉低,之后再触发都是高电平。但是rfout端口依旧输出高电平,请问下这个状态对吗?

RFOUT输出电平应该不是固定的,在datasheet中这样描述的:

The output power at the RFout pin can be programmed to various levels as well as on and off states. The output state of this pin is controlled by the RFoutEN pin as well as the RFOUT word.