LMK04906

时间:10-02

整理:3721RD

点击:

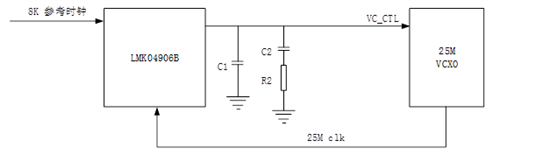

在用LMK04906做PLL时,波形输出正常,但是系统会报错。想请教下原因。相关框图及配置如下:

其中LMK04906B的IO配置为,LD管脚配置为PLL1 DLD,

STATUS_CLKIN0配置为DAC LOCKED。测试现象如下

使用25M 压控晶振7N25000009这颗器件,提供8K参考时钟之后,LMK04906B的LD输出为低,

STATUS_CLKIN0输出为低。然后我们测试了8K和25M的相位关系,如下

绿色8K,黄色 25M时钟。7N25000009的压控脚为1.65V左右。黄色和绿色不会滑动

时钟芯片的配置图。FORCE_HOLDOVER位在8K时钟有的时候,将把这位设置为0,HOLDOVER_MODE设置为disable。

8k的参考时钟吗?4906对参考的输入斜率有要求。

输入斜率有什么要求啊?请指点,谢谢。

手册第10页 slew rate