SN65LVDS391上电电流过大

大家好,

我做了一个利用SN65LVDS391实现单端信号转LVDS信号的板子,发现上电时电流很大,1.8A左右。如果将两个使能端(EN1,2和EN3,4)拉低,则电流正常;EN1,2拉高,EN3,4拉低也正常,就是只有EN3,4拉高的时候电流变大(均是通过0 ohm电阻拉高或拉低)。现在测试中通过1k ohm的电阻拉高到3.3V,EN3,4又拉不起来了(可能已经烧坏了?)。尝试了两个片子都是这样。

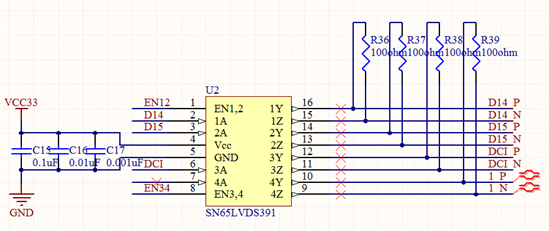

电路原理图如图1所示。请问原理图有问题吗?SN65LVDS391/387的使能端需要电阻进行拉高或拉低吗?如果是,电阻值取多大合适?

图1 SN65LVDS391原理图

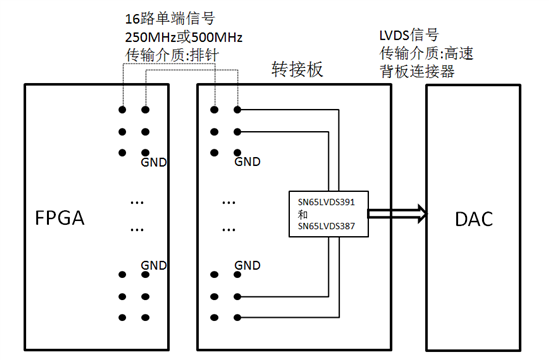

另外,当前的设计是想将一块FPGA板输出的单端信号(16路)转换成LVDS输出,送至DAC,系统示意图如图2。系统期望的速率为250MHz或500MHz,现在FPGA输出的单端信号质量就不是很好(100MHz),信号的过冲严重,转接板的地电平抖动也很厉害(Vpp 500mV左右),FPGA板的地电平抖动Vpp 260mV左右,如果复位则抖动变得很小。FPGA板是已有固定的,扩展IO口只有两个地线。

请教大家这个方案的不足,能达到预期的信号速率吗?是不是地线过少导致信号过冲和地电平的抖动?现有设计中,在FPGA的地线和转接板的地线中间串联了若干磁珠,效果有一些但仍不理想。

谢谢!

图2 系统示意图

你的意思是上电,未加输入信号和负载的时候,静态电流过大?

使能端EN不管是接上拉电阻还是直接接到VCC上,只要保证高电平即可,Vih(min)=2V。

您好,

问题解决了,重新买的芯片,上电后好用。第一次的问题仍不太清楚,两次购买的芯片封装上的文字有些不同。建议大家通过电阻作使能端的上下拉吧,我用的是10K ohm的,接到3.3V电源上,使能端得到的电压是3V以上,可以有效使能。

另外关于系统地电平噪声大的原因,应该是SSN。将未用排针有效接地(包括转接板和FPGA板),可以有效降低噪声。具体请参考《Altera FPGA/CPLD设计(高级篇)》第2版, 人民邮电出版社, EDA先锋工作室等著 第7.22节关于同步翻转噪声(SSN)的论述。

供大家参考,谢谢!