请教SN74LVC16T245芯片 上电断电时错误的高电平脉冲。

时间:10-02

整理:3721RD

点击:

最近我调试一块公司设计的板子时,碰到一个问题。在上电和断电期间,SN74LVC16T245输出管脚出现一个高电平脉冲,此脉冲会造成设备误动作。

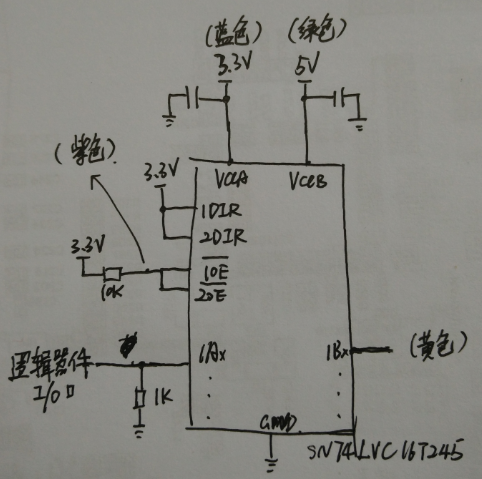

MCU电平是3.3V,通过SN74LVC16T245芯片转换为5V电平与外围设备互联。

测试电路图:

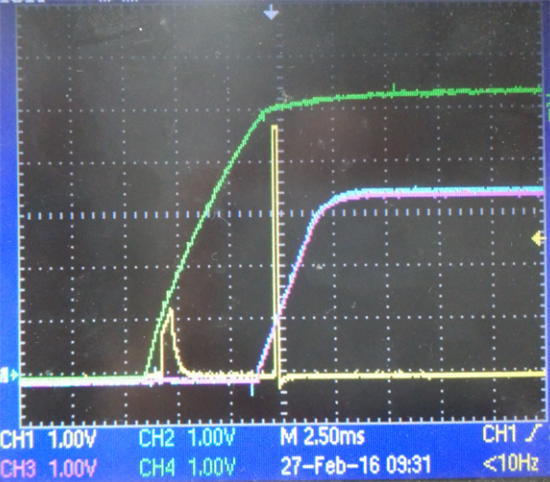

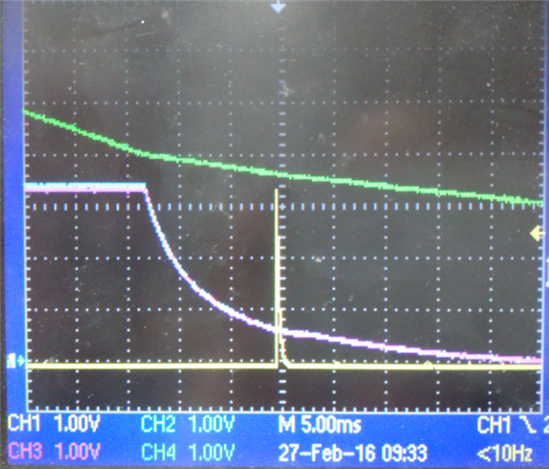

(输入引脚1Ax上电、断电时为低,示波器通道有限,没有接)

上电:

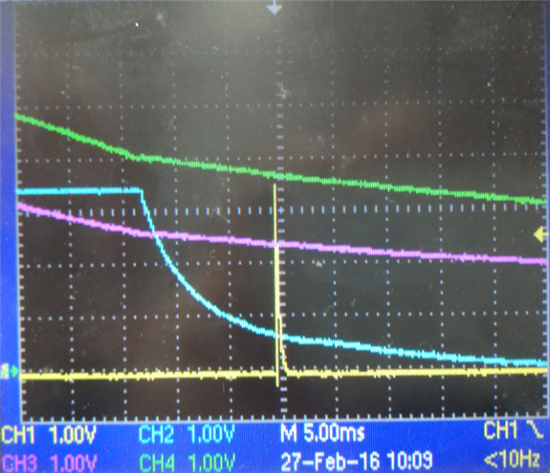

断电:

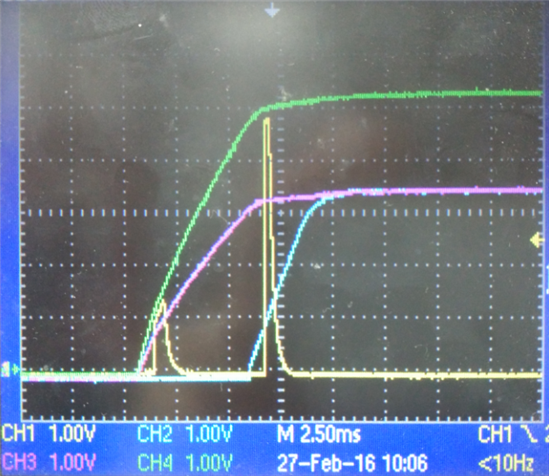

随后,我又将1\O\E\和2\O\E\ 管脚 接由5V电源分压产生的3.3V电平,波形如下

上电:

断电:

请教一下这些脉冲是什么原因造成,及解决办法

谢谢

调整上电时序,上电时,执行器最后上电,掉电时,执行器最先掉电。

谢谢你的回复,这个方法是可以行的,但是难以执行。想问一下SN74ABT16245A能否适用(A侧的输入为3.3V LVTTL电平,输出端不用考虑)?

个人觉得:你这个是外围器(5V边)上拉造成的,试着在输出端加1K下拉,我觉得可以解决问题

OE端加个电容试一试

谢谢回复,已试过,无效。

QE端加电阻到地呢?加速3.3V放电。但要注意别拉低了。

断开后级(5V),既然你输入端为0 输出端应该也是0 确定好焊接和芯片问题,这个我有遇到!

这个芯片我也在用,试了下并没有你这个问题的。

确定好前后级,如果是后级电路影响 1K强下拉 电阻至少可以拉下来一些电平,不知你后面是啥?

后级开路和后级加一个1K电阻负载 都试过了,电平同样是5V。

你的VCCA和VCCB 上电时序,斜率是怎样的?