多并联连接下的CAN网络终端电阻如何设计

时间:10-02

整理:3721RD

点击:

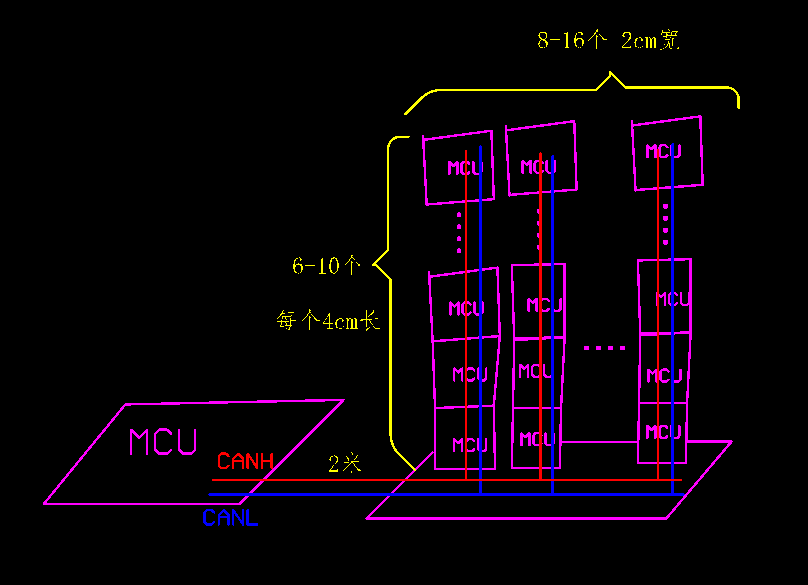

连接方式请见图片。

一个主MCU,使用CAN总线控制很多个小MCU,小MCU之间是用排针直接插在一起的,请问这个终端电阻应该怎么加啊?主控板和连接板之间用DB-9的接口和带屏蔽的线连,长度在2m以内。

这个东西是实现LED显示功能的,每个小块上有2个8*8的LED矩阵,要显示的图案会预先存在每个小块的FLASH里,工作的时候只需主MCU在can总线上广播要显示的帧数即可,要求具有较高的刷新频率,400帧每秒以上。

你好,正常的终结电阻是120欧,你这种情况介意采用split termination模式,即在每一列的最上子版处用120/n欧电阻,n为列数。

应该是120×n 是吗?

你好,我跟接口团队的can专家商量过了,你并联的网络过多,最终建议还是在你的主MCU板上做split终结,请参考附件。通过滤波来改善信号质量。

哦,好的,多谢。

很早之前就做好了,一直没想起来回复,最终的解决方案是,只在CAN总线的起始端和末端加了2个终端匹配的回路(2个60欧电阻+1个电容),中间的并联部分都悬空不管,最终的测试效果是,可以实现超过130个节点在总线上通讯,更多节点的没有测试过,不知道极限节点个数是多少,希望能帮助的有类似需求的人。