CDCE62005的两个VCO振荡频率为什么不连续?

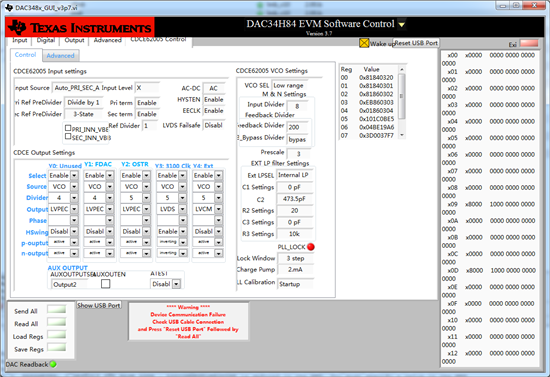

我买了TI 的DAC34H84EVM开发板,板上有一片CDCE62005的时钟芯片,但是对输入频率VCO锁定范围很窄,还不到1M,VCO的两个range居然不连续。我想用原子钟给62005做时钟参考,是10Mz的信号,但是分频比怎么调都不能锁定。默认的那组配置,25MHz虽然能锁定,但是low range只有24.6MHz~25.6MHz时锁定,high range在28.7MHz~29.9MHz时锁定,VCO不交叠,锁定范围也很窄,这样对吗?

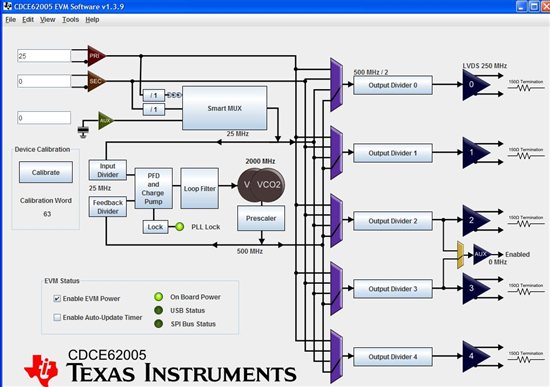

CDCE62005的VCO是连续可变的VCO1covers the range of 1.75 GHz to 2.05 GHz, and VCO2 covers the range of 2.05 GHz to 2.35 GHz. 参考分频一共有3个地方可以设置,VCO还有一个前置分频,请到TI官网下软件和资料进行研究.

按道理如果在一个频率上能锁定,比如25MHz(我用信号源给的),Locked灯可以亮,那么我连续动信号源(10K步长)就可以测出他的VCO频率,但是灯亮的范围显示VCO只能在1842~1920MHz和2148~2244MHz锁定(用频谱仪从一个输出看,再推算到prescale之前),这和手册上的1750~2046和2040~2356MHz非常不否,主要是不连续。莫非是芯片坏了?除了调整分频比外还有什么需要动的吗?

你好,你是改变参考频率而不改变配置么?

建议使用不同频率配置:

对,我看到这个界面了,但是因为DAC34H84EVM开发板上的SPI还需要控制DAC,所以应该是不能使用这个你这个界面的吧。

对,我的意思是一个分频比下,如果我改变参考频率的话,VCO应该能在它手册的这个范围内变化才对啊。当它超出这个范围时才会失锁,但是现在问题是VCO在它范围里面也会失锁。

从原理上讲不同频段vco需要重新calibration会不一样,因此改变频率建议重新配置并重新calibration.详细配置流程清参考手册36页正常流程进行配置.以确保芯片能正常工作,VCO获得正常的校准字。谢谢

yiwang:在本版另一CDCE62005的贴中有解释为什么改变参考频率导致PLL不锁定的原因,简单来说就是因为参考频率变化而环路的相位裕量变化导致Lock Time变长,当超出判决时间窗后就会导致失锁而不再去锁定了。

谢谢,这个东西我最近做了些实验,弄明白了。原来是每一步都要手工校准。比如现在是10MHz参考,先校准使其锁定,然后增加频率,比如到10.1MHz,再校准。每一次增加一小点频率,然后校准,再增加,再校准。就可以达到手册的range范围。应该是上面说的这个窗口比较小造成的。

感谢你对我们工作的支持

你好,想请教你关于cdce62005的配置问题,不知道怎么和你联系?

我的邮箱hhuang35@163.com

给你邮件,建议你讲你的问题在提问里面详细描述下,怎么配置的.如果频点不对很有可能没有锁定

我想问一下我用CDCE62005作为配置时钟,用PRI参考输入时钟,用VCXO控制输出,能保证输出与输入时钟同步吗,或者输出时钟是输入时钟的整数倍。

我想问一下我用CDCE62005作为配置时钟,用PRI参考输入时钟,用VCXO控制输出,能保证输出与输入时钟同步吗,或者输出时钟是输入时钟的整数倍。