FPGA 串行数据驱动问题

时间:10-02

整理:3721RD

点击:

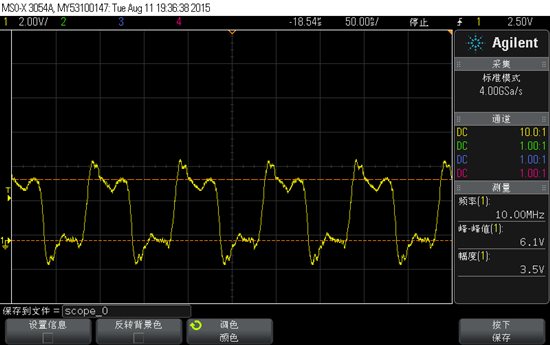

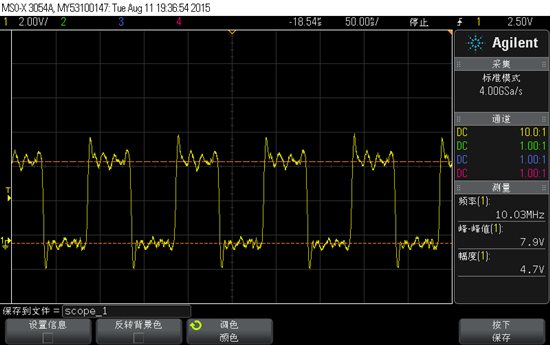

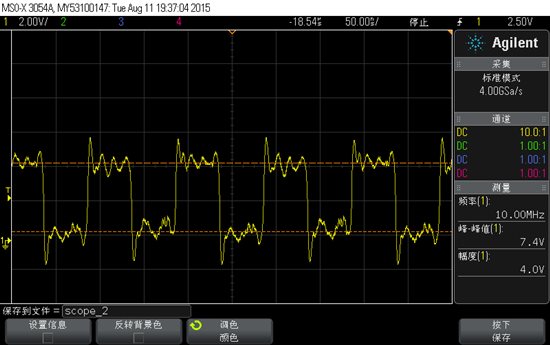

我想通FPGA作为一个控制器模拟输出一段串行数据,一个IO口作为同步时钟,另外几个IO口作为数据输出,该时钟频率为1MHz-50MHz,现在我只用了一块电平转换芯片将FPGA的3.3V电平转换成5V的CMOS电平,然而发现连接一段导线后发现,输出波形过冲太大,而且传输较高频率数据时(10MHz以上),波形严重失真,无法判断高低电平,用示波器发现,上升沿和下降沿有严重震荡问题。想知道有没有那种芯片可以作为该串口数据输出端口驱动,连接线有哪些要求?

用的哪款电平转换?导线多长就出现失真了?电平转换后5V的输出端测试波形都好的是吗?

我用了ADI一款ADG3304进行电平转换,通过排线接到另一端,然后用sn74ahc14施密特触发器进行整形,发现波形没有改善,依旧有振铃出现。超过10MHz后,波形很差

LZ可否将原理图发上来看看?

我发现电源端忘了加电容去耦,加了电容好很多。想知道施密特触发器输出通过50欧姆的同轴线传输可以传输多远?