关于ds90ub925/926q是否支持1080P的疑问,谢谢。

TI的工程师,您好,最近在为客户设计一款1080p显示设备时遇到一个问题,客户的显示要求为1280×1024×60Hz,传输只能有一对差分数据线,最后选择到ds90ub925/926q这对芯片,但是芯片标称只支持720p,通过细致查阅手册,发现这款芯片的PCLK是支持到85MHz的,带宽也到达了2.975Gbps,而我们的设计最大83MHz,带宽需求1.8Gbps,芯片在这两项重要指标是满足要求的,我目前主要疑问还是在分辨率上,通过查阅手册,控制信号HS,VS,DE的描述中有“130个PCLK传输2次”的说明,但是具体含义不是很理解,希望TI工程师帮我解惑,谢谢。

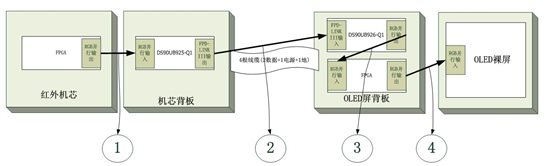

附上设计方案

1280×1024×60Hz的话要求pixel clock的频率至少为108MHz, 而ds90ub925/926q的PCLK最大频率范围为85Mhz,所以是不支持1280×1024×60Hz。

85Mhz的话能够支持的分辨率为1280 × 720p@60Hz。

shangming yang

控制信号HS,VS,DE的描述中有“130个PCLK传输2次”的说明,但是具体含义不是很理解,希望TI工程师帮我解惑,谢谢。

数据手册中没有给出HS, VS以及DE的时序,你可以用示波器量下PCLK,HS,VS,DE的时序,应该就好理解了,这句话的意思应该是说对于HS来说,经过130个PCLK,HS和DE信号从高到低或者从低到高变化两次,而VS在130PCLKs内只变化一次。

谢谢Kailyn工程师的回复。

由于目前电路原理还在设计论证阶段,所以手头没有实物可以测量,而且工期紧张,争取设计能够一次成功。

我纠结HS,VS,DE的原因如下:

前端传感器给出的图像数据通过FPGA给到925,图像分辨率其实是1280×1024,帧频60Hz,由此可以计算出时钟需求的下限是1280×1024×60≈78MHz,图像数据是24bit的,带宽需求下限是78MHz×24bit=1.887Gbps,这两个指标是925/926的性能可以保证的,加上FPGA送给925需要一些额外的像素开销,也应该是满足芯片要求的。

HS, VS以及DE三个控制信号,我理解是RGB标准时序,也就是说FPGA通过控制这三个信号其实是可以达到裁剪分辨率的目标的,也就是说,在传一帧图像时,HS持续有效1024行,DE每行持续有效1280列(也就是1280个PCLK),VS在每帧头有效一次(芯片要求至少130PCLK),这样我就在满足芯片性能的前提下传输了一帧1280×1024分辨率的图像,而接收端,926可以将这个时序恢复出来,FPGA接收之后再送OLED显示。

而925/926芯片标称的720p,我认为是广播电视标准的1920×720,这个标准的时钟要求是108MHz,而实际中我并不是采用这一分辨率,只要芯片本身不会对HS, VS以及DE做强制处理(比如芯片内部对每帧内HS变高个数进行计数,一旦超过720,就强制中断传输,或者对每行DE有效个数计数,一旦高于1920,就强制中断传输,等等),我认为都是可以达到我的设计目的的。

以上个人理解,不知道正确与否,还请解惑,谢谢。