CDCM6208V1 输入时钟连接

请教各位TI 工程师一个问题。

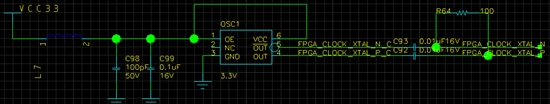

我采用差分晶振作为该芯片的时钟源,接入到sec_ref上,具体连接如下:

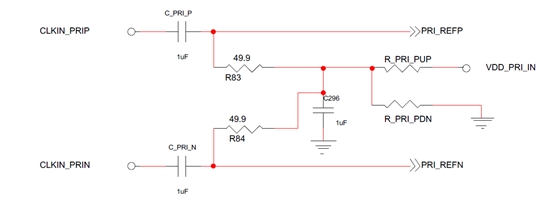

而datasheet第78页上显示需要给输出加上1.2V的偏置,而且端接电容是1UF。

1. 1.2V的偏置是必要的吗?我参考了研华出的TCI6638k2h,有些加了有些没加。

2. 端接的电容值有什么要求?我在之前类似的设计中多采用0.01uf或者0.1uf,运行也比较良好。

请各位专家不吝赐教!

看一下这个连接

http://www.ti.com/lit/ug/scau049a/scau049a.pdf

有完整的SCH图。里面的隔直电容就不是1u的

1. 1.2V的偏置是必要的吗?我参考了研华出的TCI6638k2h,有些加了有些没加。

A: AC耦合的话,1.2V的偏置是有需要加的,当两个不同电平之间耦合连接时,一般才有AC耦合,然后保证输出的共模电压满足接收端的共模电压。数据手册中给出的意思是说,如果差分信号的共模电压和CDCM6208的共模输入电压电平不一致,建议加上1.2V的偏置,像你说的研华给出的就没有加,应该是相同电平直接耦合连接吧。

2. 端接的电容值有什么要求?我在之前类似的设计中多采用0.01uf或者0.1uf,运行也比较良好。

A: 我见到的最多的AC耦合电容也是0.1uF。

Chen,你好!

关于CDCM6208的使用目前还有一些问题想请教一下,就不另发新帖了。我设计的板卡上,CDCM6208用于给Xilinx的K7芯片提供GTX参考时钟,采用PIN_MODE 7-V1,8路时钟输出都为LVDS 125MHz。我发现,当两个GTX采用同一路时钟时,他们之间做互回环是没问题的,125M下误码率在10exp(-12)水平上。但是一旦两个GTX采用两路不同的参考时钟输入,链路误码率就会直线上升,误码率高达10exp(-6)。我初步认为是时钟同步的问题,于是在程序里给SYNCN引脚做了一个复位脉冲,维持大概2.5ms后拉高,互回环实验发现误码率仍然维持在10exp(-6)这个水平。

现在的这个误码率显然不适合做板间通信了。那么当每一路时钟输出的配置参数都相同的时候,什么因素会导致不同时钟输出链路之间的差异呢?请chen和各位工程师能够帮忙分析一下!

两路不同的输入参考时钟jitter是一样的吗?

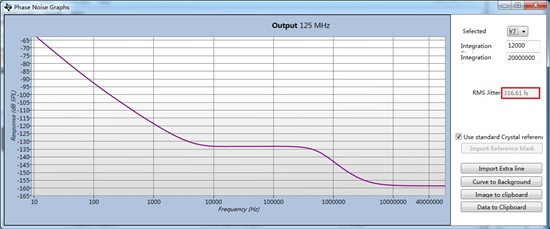

TI的CDCM6208 EVM Software给出的PIN_MODE V1-7输出时钟jitter如下:

按照它给出的数据显示,每一路输出的jitter都是316.61fs。

请问采用SYNCN对输出同步之后所有路都是同时输出的么?会否有链路间的延时?