DP83640 LINK STATUS一直为0

首先复位PHY,往0x00寄存器写0x8000;然后读0x00,内容为0x3100。读0x10,内容为0x0000;然后读0x01的0x0004位为0。程序如下:

do

{

timeout++;

} while (!(ETH_ReadPHYRegister(PHYAddress, PHY_BSR) & PHY_Linked_Status) && (timeout < PHY_READ_TO));

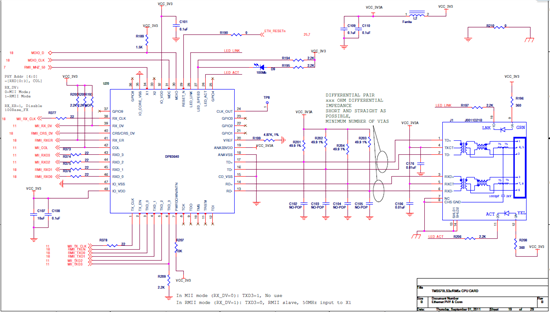

直到超时,0x01寄存器的第4位一直为0,请问怎么回事?PHY与RJ45连接,连接方式与官网参考电路一致。还有,想问一下那个LED灯怎么接?具体电路如图所示。

灯的接法可以参考下图. 另外从电路图看,你用的应该是RMII接口, pin 6应该是电阻拉倒地,还有你需要检查下参考时钟是不是50Mhz,检查下clock out引脚是不是50Mhz。

我用的是Slave Master模式,Pin6应该是TXD3,应该是上拉吧。。。我把TXD2下拉1k电阻了。那个RX_CLK,和TX_CLK有50MHz输出。。。CLK_OUT输出25MHZ,RX_CLK在复位时是25Mhz的时钟,请问这样我改如何调试?

您图中E\G是指的地吗?LED_LINK信号信号上电不是要被采样吗?我现在LED_ACT和LED_SPEED是按照您的接法连接的,只有LED_SPEED常亮,其他的不亮。。。

我给你的前一张图是MII接口的,只是让你看看灯的接法。

你对着下面这张图看看,是我们EVM上的电路。

你好!我想请教下,pin6脚下拉式Slave模式,悬空就应该是Master模式吧!有Slave Master这种模式吗?

没有。

为什么我的MII_MODE脚接上拉了,可他的管脚还是低电平啊……?是不是芯片有问题啊?

还有就是,第40引脚(SRS_DV)不接上拉可以吗?

求快回……!谢谢了……!

RBR寄存器第五位设置正确吗?SRS_DV内部已有上拉(PU)

你好!能帮我解答下这个问题吗?谢谢了…………!

http://www.deyisupport.com/question_answer/analog/interface_and_clocks/f/59/t/50941.aspx

今天早上看到你的帖子,但是ti这个一直登陆不上,也就回复不了。。。对,但是没有有Slave Master这种模式,只有RMII Slave和RMII Master模式

这个只是采样的时候使用,你可以看看相应的寄存器里的值是否是你需要的。

恩恩,能不能帮我看看这个问题啊…………?谢谢了……!

http://www.deyisupport.com/question_answer/analog/interface_and_clocks/f/59/t/50872.aspx

您好能麻烦您帮我看看我这个图能支持PTP吗?GPIO部分的连接我还不是很清楚,使用的是RMII从模式,把GPS的1PPS连接到了GPIO9上,还有几个GPIO连接到了FPGA上,我感觉是用来触发时间的事件消息的,麻烦帮我解释一下好吗,感激不尽

您好能麻烦您帮我看看我这个图能支持PTP吗?GPIO部分的连接我还不是很清楚,使用的是RMII从模式,把GPS的1PPS连接到了GPIO9上,还有几个GPIO连接到了FPGA上,我感觉是用来触发时间的事件消息的,麻烦帮我解释一下好吗,感激不尽