3.3V时钟如何转成5V时钟?

DSP(VC33)作为主处理器,FPGA作为从处理器。为了实现两者时钟同步,外部采用了一片3.3V的有源晶振,但FPGA的IO电源为5V,请问如何转换?

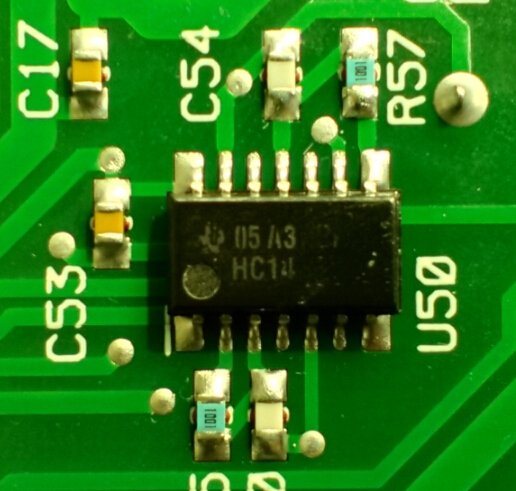

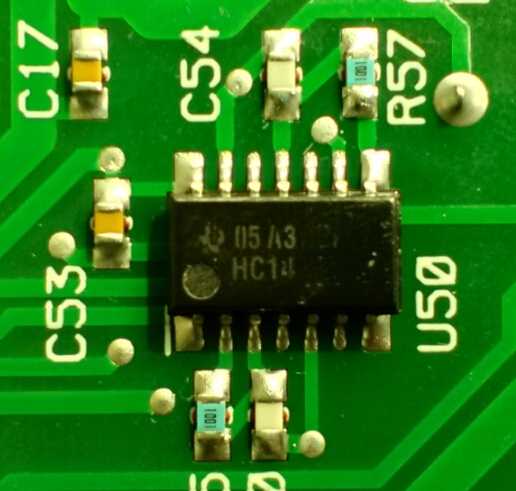

考虑过在FPGA时钟输入与有源晶振输出之间加一片HC14,利用施密特整形,但HC14的V+最大值正好在3.3V左右,余量很小,电路的可靠性要求高,请问该如何解决?

Fangming,

你看一下FPGA的IO指标,一般5V的TTL电平对>2.4V的电平就认为是高了,如果指标上满足你可以直接用3.3V的晶振。

如果不满足,你可以找一个类似于74HC245这样的电平转换芯片将3.3V转为5V。

首先,感谢您的解答。

还有一些疑问,74HC245类似这样的芯片,HIN的值一般是在2.4-3.1之间(4.5V供电,数据手册上的,我没有记错的话),2.4只是最小值,我疑惑在不同的环境下,比如极端温度,5V供电的前提下,会不会出现3.3V正好也认为是低的情况(临界值)。所以,想请教大家,是否有其他保险的办法?

这个问题的来源:我的板子上有3.3V(DSP)和5V(FPGA),希望两者时钟同步。

3.3V时钟供5V FPGA也是如此,我怕极端情况下会出现3.3V正好是HIN的临界值,所以想找个可靠的办法。

Fanming,

对于芯片来说,器件手册上给出的指标都是要考虑器件的工作温度范围的,所以只要温度没有超过器件的温度范围不必担心芯片指标在高温的可靠性。

请问这是什么芯片?详细的PDF文件

请问这是什么芯片?详细的PDF文件

请问这是什么样的芯片?谢谢?

请问这是什么样的芯片?谢谢?

亲;这是高速5V工艺COMS六施密特反相器。

这款的型号为SN74HC14。六路施密特触发器,3.3V转5V的单通道的电平转换可考虑TXS0101这款。

你的晶振的频率是多少?频率太高的话,可以用时钟buffer进行3.3到5V的转换

1. FPGA的型号?看看FPGA的IO标准里面,有没有3.3V标准?

2. 有源晶振的型号?有源晶振的IO标准,一般是H>=0.9VCC=2.97V,L<=0.1VCC=0.33V。而5V的IO标准一般是H>=2.0V(LVTTL)、2.4V(TTL),L<=0.4V(LVTTL)、0.8V(TTL)。可以看出,有源晶振与5V是直接兼容的。

上述的 1、2 情况里,只要有1个成立,就无需添加电平转换芯片了。