关于DP83620和AM335X配合使用的硬件连接问题。

在我的设计中,使用了两个光口,采用的设计为TI的AM3354+DP83620+安华高的5803Z。

接口方面,我使用了3354自带的RMII接口,两个PHY各占用一个RMII接口,采用的模式为PHY主模式,时钟设计为25M晶振.

由于考虑到单双路的问题,我们把两个ETH是分开的,但我总觉得这个图哪里不对,在这种应用中,DMIO和MDC是必须的吗?有什么不对的地方请各位批评指正!

Hi Pengfei,

1)DP83620 TX+,TX- 与电容C12,C13间加50欧姆电阻上拉到V3.3

2)去掉R2。

3)MDC,MDIO 不是必须的。

谢谢您的回复!

DP83620的TX要上拉这个我可以理解,但是这个阻值有什么依据吗?还有那个C12,C13我不是很清楚这个器件是做什么用的,对该器件本身有没有什么要求?例如误差、温漂、封装等,AFBR5803侧我是参考了该器件的Datasheet,参考附件。

另外MDC和MDIO我一直是百思不得其解,根据资料显示,这两个管脚一个是时钟,一个是数据,它主要是MAC对PHY执行一些读写的命令。再看其他人的DP83640,DP83848的设计,他们都是使用了这两个管教,如果不使用这两个脚,我的PHY的地址MAC怎么去认定呢,还有PHY的寄存器MAC怎么去操作呢?MAC地址又放在哪里呢?

(鉴于本人刚解除ETH设计这一块,可能有些问题比较肤浅,但我不是说什么资料都不看的伸手党,再者边上也没什么人可以请教,英语也不太好,所以请谅解!)

Hi pengfei,

1)tx+,tX- 是CML电平,所以需要上拉。

2) 如果mac 要对phy执行一些读写命令,当然要用MDC,MDIO. 如果不读写,就不需要了。至于地址可以用phyad进行配置。

PHYAD怎么设置呢?在DP83620的Datasheet视乎没有提到这一点

在datasheet的5.5节“PHY ADDRESS” 有描述,pin42---46

最近也在使用DP83620,光模块使用的AFBR5803ATQZ,发现会出现bad pakage,测量发现光模块的发送脚(管脚7、8)上的电平不满足LVPECL电平的要求,直流电平不是2V,在1.5V左右,正常的LVPECL电平直流电平大概在2V,电路的形式和参数都是根据DP83620的demo板来的,不知道该怎么样处理?

另问楼主的电路实际工作状态怎么样?

谢谢!

Jeff Wang 你好,你说MDC MDIO 不是必须的,可以给点建议吗? 如何在代码取出mdio

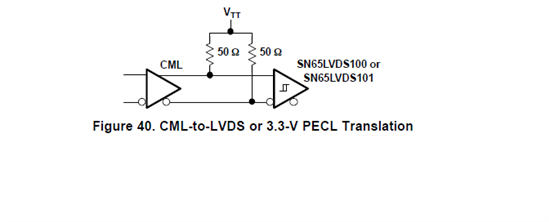

1.5V 左右是CML电平,可按照CML 到LVPECL电平耦合的方式来连接 ,参考SN65LVDS101datasheet中给出的CM

L 到LVPECL耦合的连接方式即可。

L 到LVPECL耦合的连接方式即可。