cdce62005的loop filter起什么作用啊?

时间:10-02

整理:3721RD

点击:

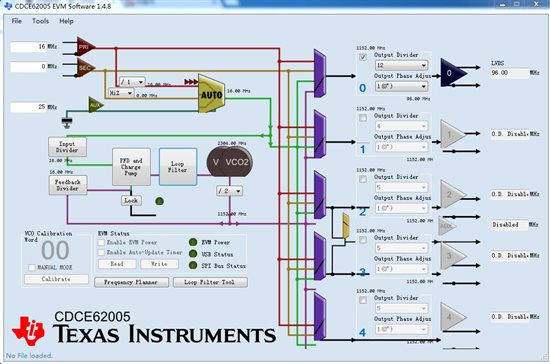

我们的板子用16MHz的输入时钟,生成96MHz的输出时钟,用ti的配置软件GUI进行配置;

用Frequency Planner 进行了计算并应用,可以输出96MHz的时钟,如图:

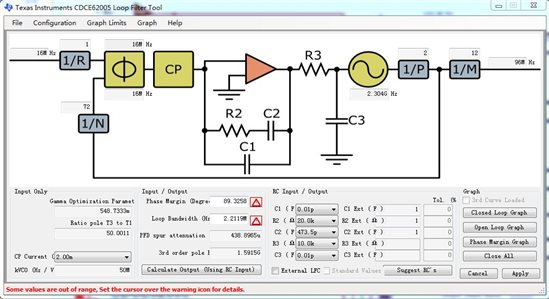

但是GUI中的Loop Filter点进去,再点开loop filter tool,会有两个地方警告,如图:

1、请问这个有关系吗?一直不明白loop filter到底起什么作用?这些电阻电容的值会对影响什么?难道要自己手动调整吗?

2、我对输出0,1,2,3路时钟都是同样的输出96MHz,都是用LVDS输出,但是用示波器量发现输出时钟的峰峰值差蛮大,不知道是什么原因?

1.loop filter是用来调整PLL的相噪的,简单来说就是用一个合适的LOOP FILTER才可以得到最佳的jitter性能。LOOP FILTER不合理会增大抖动,甚至使得PLL失锁,你图中的参数配置,相位裕度太大,一般60-70度左右就可以了,环路带宽要根据你的参考时钟来定,如果参考相噪比较差,环路带宽建议设低一些。电阻电容决定了环路滤波器的零极点,从而影响环路带宽和PLL上锁时间等。建议楼主看一些PLL基础知识

2.请检查输出和输入有没有做阻抗匹配,是否各路的阻抗匹配都一样

今天配置后,发现输出时钟总是只有86MHz;但是如果直接通过输出分频时钟,不通过VCO,输出时钟就是对的。这是什么原因啊?我的输出接的33欧的电阻,用的16M的AUX单端输入时钟。

你用示波器量一下lock管脚。读寄存器看看lock了没有

量了也读了,都是0